# **PIO 01**

**Peripheral Input Output TTL**

# TECHNICAL MANUAL

Standrad Eurocard format 100x160 mm; interface to **ABACO**<sup>®</sup> **Industrial BUS**; **96** TTL I/O signals; **twelve** 8 signals parallel ports managed by four **PPI 82C55**; **6** standard **ABACO**<sup>®</sup> I/O **20 pins** connectors; **watch dog** circuitery capable to work in astable and monostable mode and intervent time settable between **1 msec** and **16,50 sec** through jumper and trimmer; LED to signal watch dog circuitery activation; **wait** circuitery to introduce **3**, **5** or **8** wait cycles in I/O operations; selection of I/O mapping through **2 dip switches** on board; addressing space taken as low as 16 contiguous bytes; management of address BUS **8** or **16÷20** bits wide, selectable through jumpers; direct interface to the field modules type **FBC**, **OBI**, **RBO**, **TBO** or **XBI**; direct inferface to the parallel operator panels **QTP 24P** and **QTP 16P**; unique power supply +**5Vdc**

# DOCUMENTATION COPYRIGHT BY grifo<sup>®</sup>, ALL RIGHTS RESERVED

No part of this document may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means, either electronic, mechanical, magnetic, optical, chemical, manual, or otherwise, without the prior written consent of **grifo**<sup>®</sup>.

# IMPORTANT

Although all the information contained herein have been carefully verified, **grifo**<sup>®</sup> assumes no responsability for errors that might appear in this document, or for damage to things or persons resulting from technical errors, omission and improper use of this manual and of the related software and hardware.

**grifo**<sup>®</sup> reserves the right to change the contents and form of this document, as well as the features and specification of its products at any time, without prior notice, to obtain always the best product.

For specific informations on the components mounted on the card, please refer to the Data Book of the builder or second sources.

# SYMBOLS DESCRIPTION

In the manual could appear the following symbols:

Attention: Generic danger

Attention: High voltage

# **Trade Marks**

**GPC**<sup>®</sup>, **grifo**<sup>®</sup> : are trade marks of **grifo**<sup>®</sup>. Other Product and Company names listed, are trade marks of their respective companies.

# **GENERAL INDEX**

| INTRODUCTION                                         | 1  |

|------------------------------------------------------|----|

| CARD VERSION                                         | 1  |

| GENERAL DESCRIPTION                                  | 2  |

| ADDRESSING AND INTERFACEMENT                         | 4  |

| CONTROL LOGIC                                        | 4  |

| WATCH DOG                                            | 4  |

| WAIT STATE GENERATOR                                 | 4  |

| TTL I/O LINES                                        | 5  |

| TECHNICAL FEATURES                                   | 6  |

| GENERAL FEATURES                                     | 6  |

| PHYSICAL FEATURES                                    | 6  |

| ELECTRIC FEATURES                                    | 7  |

| INSTALLATION                                         | 8  |

| CONNECTIONS                                          | 8  |

| CN1 - PORT B OF PPI 82C55 SECTIONS 1 AND 2 CONNECTOR | 8  |

| CN5 - PORTS A AND C OF PPI 82C55 SECTION 1 CONNECTOR | 10 |

| CN3 - PORTS A AND C OF PPI 82C55 SECTION 2 CONNECTOR | 12 |

| CN2 - PORT B OF PPI 82C55 SECTIONS 3 AND 4 CONNECTOR | 14 |

| CN6 - PORTS A AND C OF PPI 82C55 SECTION 3 CONNECTOR | 16 |

| CN4 - PORTS A AND C OF PPI 82C55 SECTION 4 CONNECTOR | 17 |

| K1 - ABACO <sup>®</sup> BUS CONNECTOR                | 18 |

| VISUAL FEEDBACK                                      | 20 |

| POWER SUPPLY                                         | 20 |

| BOARD CONNNECTIONS                                   | 20 |

| RESET CIRCUITRY                                      | 20 |

| JUMPERS                                              | 21 |

| 6 PINS JUMPER                                        | 21 |

| 2 PINS JUMPERS                                       | 22 |

| 3 PINS JUMPERS                                       | 22 |

| 8 PINS JUMPERS                                       | 24 |

| WAIT STATE GENERATOR                                 | 24 |

| RESET AND WATCH DOG                                  | 25 |

| DIGITAL I/O INTERFACES                               | 26 |

| HARDWARE DESCRIPTION                                 | 27 |

| BOARD MAPPING                                        |    |

| INTERNAL REGISTERS ADDRESSING                        | 30 |

| PERIPHERAL DEVICES SOFTWARE DESCRIPTION              | 31 |

| WATCH DOG                                            | 31 |

| PPI 82C55                                            | 31 |

| (-abaco_●•)(bu/)                    | - grifo <sup>®</sup> ITALIAN TECHNOLOGY |

|-------------------------------------|-----------------------------------------|

| EXTERNAL CARDS                      |                                         |

| BIBLIOGRAPHY                        |                                         |

| APPENDIX A: ELECTRIC DIAGRAMS       | S A-1                                   |

| <b>APPENDIX B: ON BOARD COMPONE</b> | CNTS DESCRIPTION B-1                    |

| APPENDIX C: ALPHABETICAL INDE       | XC-1                                    |

# **FIGURES INDEX**

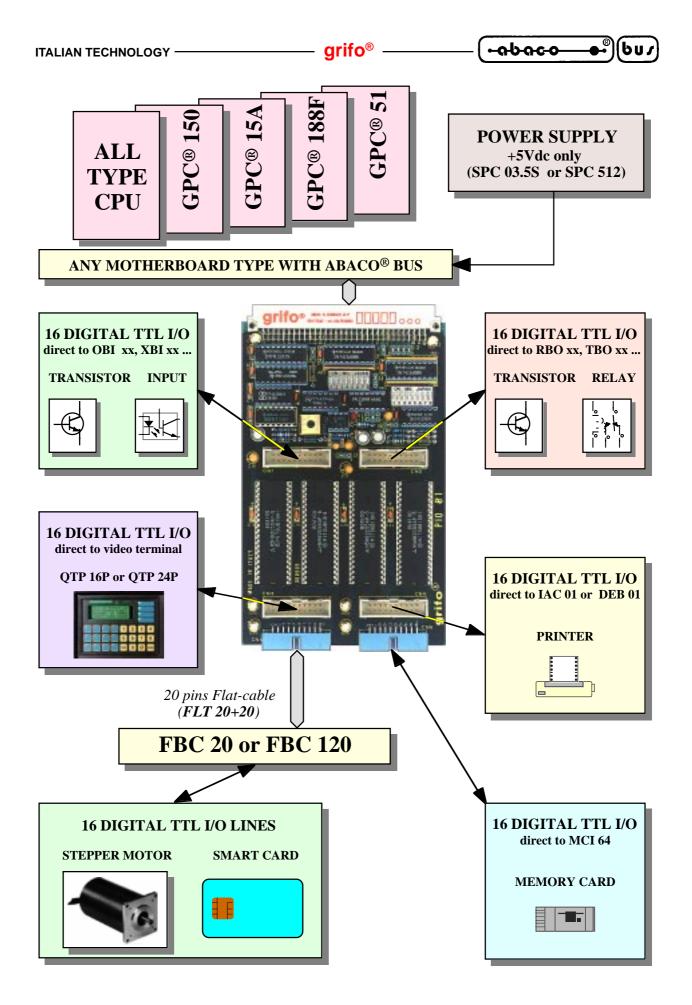

| FIGURE 1: BLOCK DIAGRAM                                            | ģ |

|--------------------------------------------------------------------|---|

| FIGURE 2: COMPONENTS MAP 7                                         | ' |

| FIGURE 3: CN1 - PORT B OF PPI 82C55 SECTIONS 1 AND 2 CONNECTOR     | j |

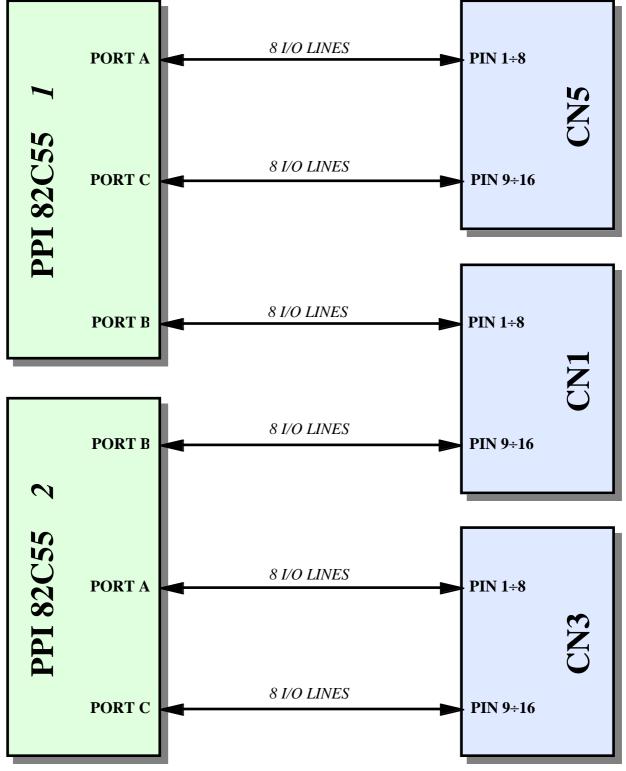

| FIGURE 4: PPI 82C55 SECTIONS 1 AND 2 BLOCK DIAGRAM                 | ) |

| FIGURE 5: CN5 - PORTS A AND C OF PPI 82C55 SECTION 1 CONNECTOR 10  | ) |

| FIGURE 6: CONNECTORS, DIP SWITCHES, LED AND TRIMMER LOCATIONS 11   |   |

| FIGURE 7: CN3 - PORTS A AND C OF PPI 82C55 SECTION 2 CONNECTOR 12  |   |

| FIGURE 8: CARD PHOTO                                               | ģ |

| FIGURE 9: CN2 - PORT B OF PPI 82C55 SECTIONS 3 AND 4 CONNECTOR 14  | , |

| FIGURE 10: PPI 82C55 SECTIONS 3 AND 4 BLOCK DIAGRAM                | , |

| FIGURE 11: CN6 - PORTS A AND C OF PPI 82C55 SECTION 3 CONNECTOR 16 | ) |

| FIGURE 12: CN4 - PORTS A AND C OF PPI 82C55 SECTION 4 CONNECTOR 17 | ' |

| FIGURE 13: K1 - ABACO® BUS CONNECTOR 18                            | , |

| FIGURE 14: VISUAL FEEDBACK TABLE                                   | ) |

| FIGURE 15: JUMPERS SUMMARIZING TABLE 21                            |   |

| FIGURE 16: 6 PINS JUMPERS TABLE                                    |   |

| FIGURE 17: 2 PINS JUMPERS TABLE                                    | ł |

| FIGURE 18: 3 PINS JUMPERS TABLE                                    | i |

| FIGURE 19: JUMPERS LOCATION                                        | į |

| FIGURE 20: 8 PINS JUMPERS TABLE                                    | , |

| FIGURE 21: INTERNAL REGISTERS ADDRESSING TABLE                     | ) |

| FIGURE 22: POSSIBLE CONNECTIONS DIAGRAM                            | , |

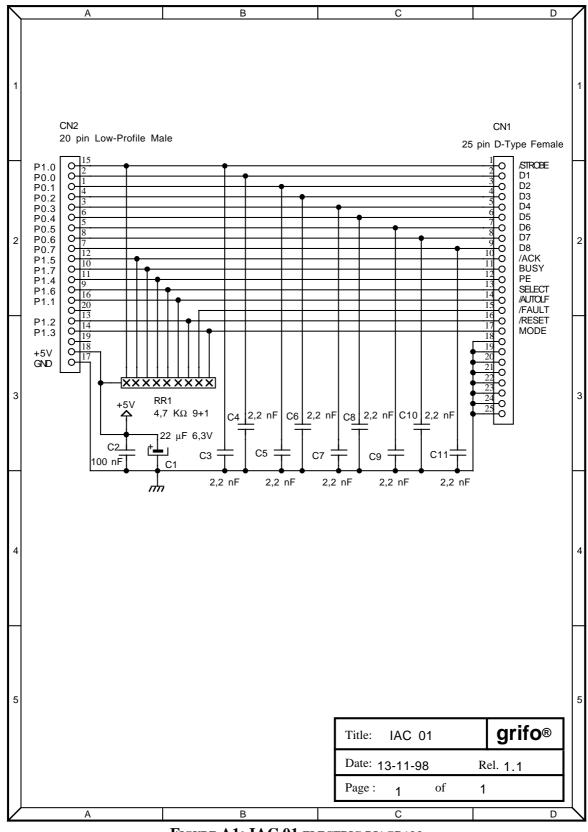

| FIGURE A1: IAC 01 ELECTRIC DIAGRAM                                 |   |

| FIGURE A2: KDx x24 ELECTRIC DIAGRAM A-2                            |   |

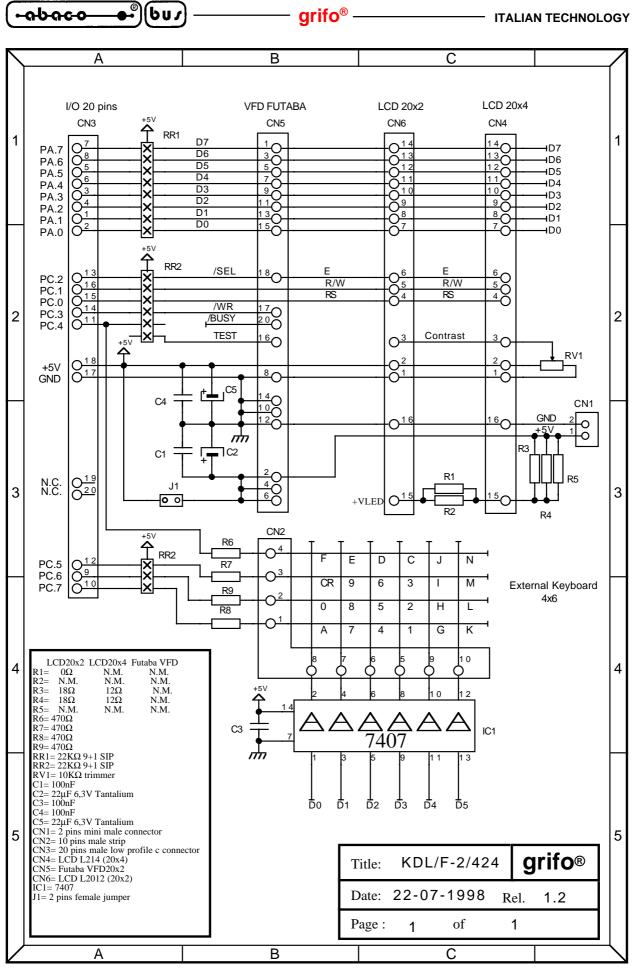

| FIGURE A3: QTP 16P ELECTRIC DIAGRAM A-3                            | ģ |

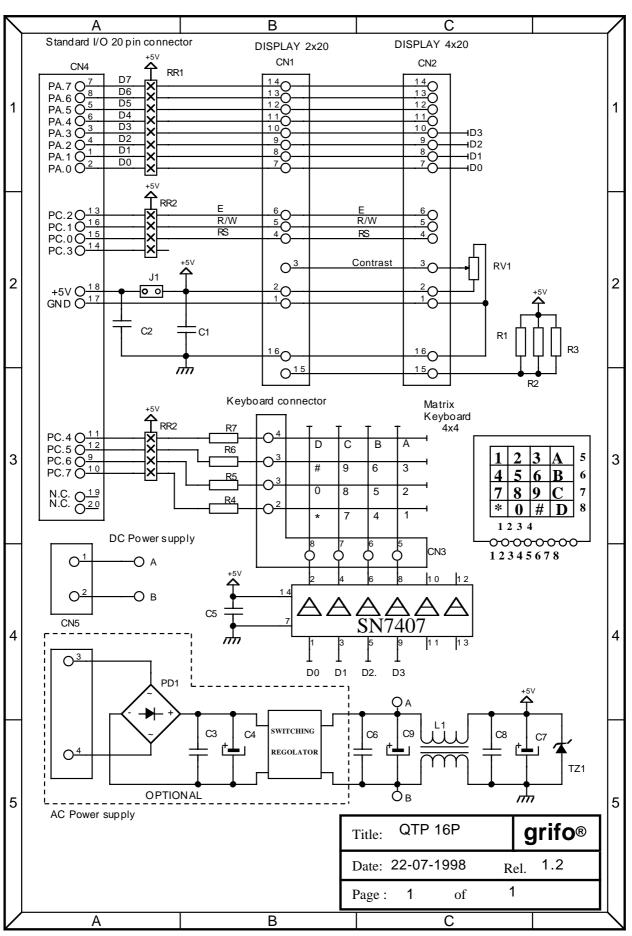

| FIGURE A4: QTP 24P ELECTRIC DIAGRAM - PART 1 A-4                   | ļ |

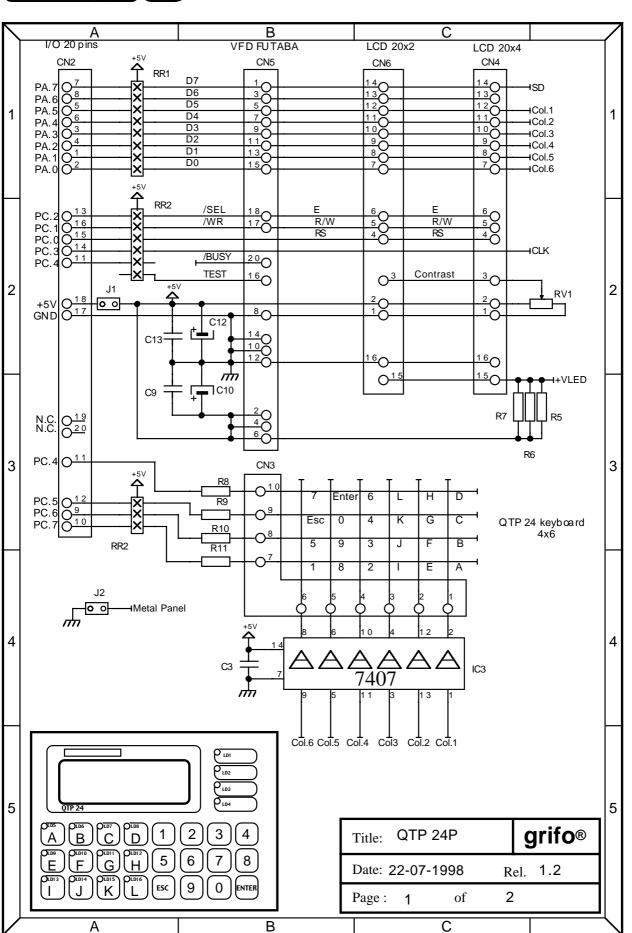

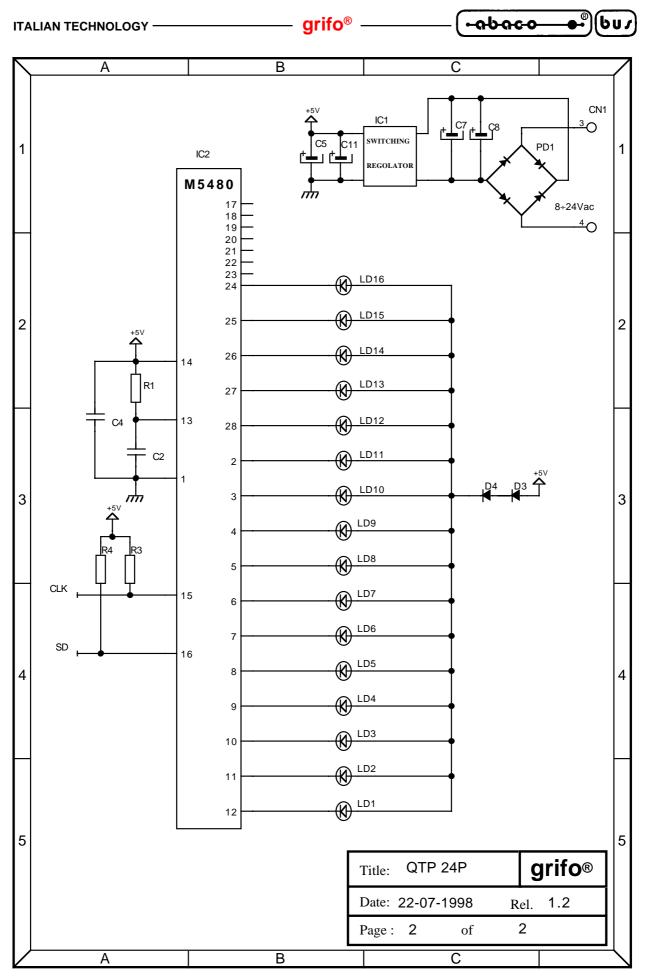

| FIGURE A5: QTP 24P ELECTRIC DIAGRAM - PART 2 A-5                   | í |

- 🕞

#### INTRODUCTION

The use of these devices has turned - IN EXCLUSIVE WAY - to specialized personnel.

The purpose of this handbook is to give the necessary information to the cognizant and sure use of the products. They are the result of a continual and systematic elaboration of data and technical tests saved and validated from the manufacturer, related to the inside modes of certainty and quality of the information.

The reported data are destined- IN EXCLUSIVE WAY- to specialized users, that can interact with the devices in safety conditions for the persons, for the machine and for the environment, impersonating an elementary diagnostic of breakdowns and of malfunction conditions by performing simple functional verify operations, in the height respect of the actual safety and health norms.

The informations for the installation, the assemblage, the dismantlement, the handling, the adjustment, the reparation and the contingent accessories, devices etc. installation are destined - and then executable - always and in exclusive way from specialized warned and educated personnel, or directly from the TECHNICAL AUTHORIZED ASSISTANCE, in the height respect of the manufacturer recommendations and the actual safety and health norms.

The devices can't be used outside a box. The user must always insert the cards in a container that rispect the actual safety normative. The protection of this container is not threshold to the only atmospheric agents, but specially to mechanic, electric, magnetic, etc. ones.

To be on good terms with the products, is necessary guarantee legibility and conservation of the manual, also for future references. In case of deterioration or more easily for technical updates, consult the AUTHORIZED TECHNICAL ASSISTANCE directly.

To prevent problems during card utilization, it is a good practice to read carefully all the informations of this manual. After this reading, the user can use the general index and the alphabetical index, respectly at the begining and at the end of the manual, to find information in a faster and more easy way.

#### CARD VERSION

This handbook makes reference to boards version **030392** and following ones. The validity of the information contained in this manual is subordinated to the card version, so the user must always verify the correct correspondence between the notations. On the card the release number is present in more points both on printed diagram (serigraph) and printed circuit (for example near connector CN3 on the component side).

GENERAL DESCRIPTION

6u*s*

abaco

**PIO 01** (Peripheral Input Output TTL) is a powerful peripheral card featuring the standard Eurocard format and interfacace to **ABACO**<sup>®</sup> industrial BUS. This digital peripheral card implements 96 TTL I/O lines and can be driven through one of the numerous **GPC**<sup>®</sup> serie intelligent cards produced by **grifo**<sup>®</sup>.

- arifo®

On board are installed four section each of which manages 24 TTL I/O lines, such lines are available on six comfortable standard **ABACO**<sup>®</sup> I/O 20 pins connectors.

The on board hardware provides TTL I/O lines; should the user need a different modality of interfacement then he/she can take advantage of a complete serie of signals adaptation modules, such the **RBO**, **TBO**, **OBI** or **XBI** series modules.

These **BLOCK** family modules can realize most of the common interfacement combinations used in industrial environment.

The intelligent control board (**GPC**<sup>®</sup> serie) is encharged with setting the employ mode of all the lines so it must decide also their directionality. To read the inputs and to set the outputs it is enough to perfrom simple read and write operations to bytes.

The 96 I/O lines can be managed simply as parallel ports or can be programmed to work in more sophisticated ways. The four PPI 82C55, that perform the hardware management of the lines, can be programmed to work in many different modalities, allowing the user to deal with several kinds of problematics.

The board also features a Watch Dog circuitery which can reach the intelligent control board directly through the **ABACO**<sup>®</sup> BUS. An opportune management of this section allows to increase the security of all the system.

When a **Power-On** or a **Reset** occours **PIO 01**, by means of a specific cirucitery, configures all the 96 lines as inputs, to warrant the absence of uncertainty about the initial status.

The board takes only 16 bytes of addressing space and can operate on a BUS that features 8 or 16÷20 bits of address word; configuration is made through comfortable jumers.

**PIO 01** is the ideal component to employ for all the system automation problems where it is required to manage a high number of logical inputs and outputs or wherever a very high number of TTL lines is needed.

Overall features of PIO 01 are:

- Standard Eurocard format 100x160 mm

- Interface to ABACO® Industrial BUS

- 96 TTL I/O signals

- Twelve 8 signals parallel ports managed by four PPI 82C55

- 6 standard ABACO<sup>®</sup> I/O 20 pins connectors

- Watch dog circuitery capable to work in astable and monostable mode and intervent time settable between 1 msec and 16,50 sec through jumper and trimmer

- LED to signal watch dog circuitery activation

- Wait circuitery to introduce 3, 5 or 8 wait cycles in I/O operations

- Selection of I/O mapping through 2 dip switches on board

- Addressing space taken as low as 16 contiguous bytes

- Management of address BUS 8 or 16÷20 bits wide, selectable through jumpers

- Direct interface to the field modules type FBC, OBI, RBO, TBO or XBI

- Direct inferface to the parallel operator panels QTP 24P and QTP 16P

- Unique power supply +5Vdc

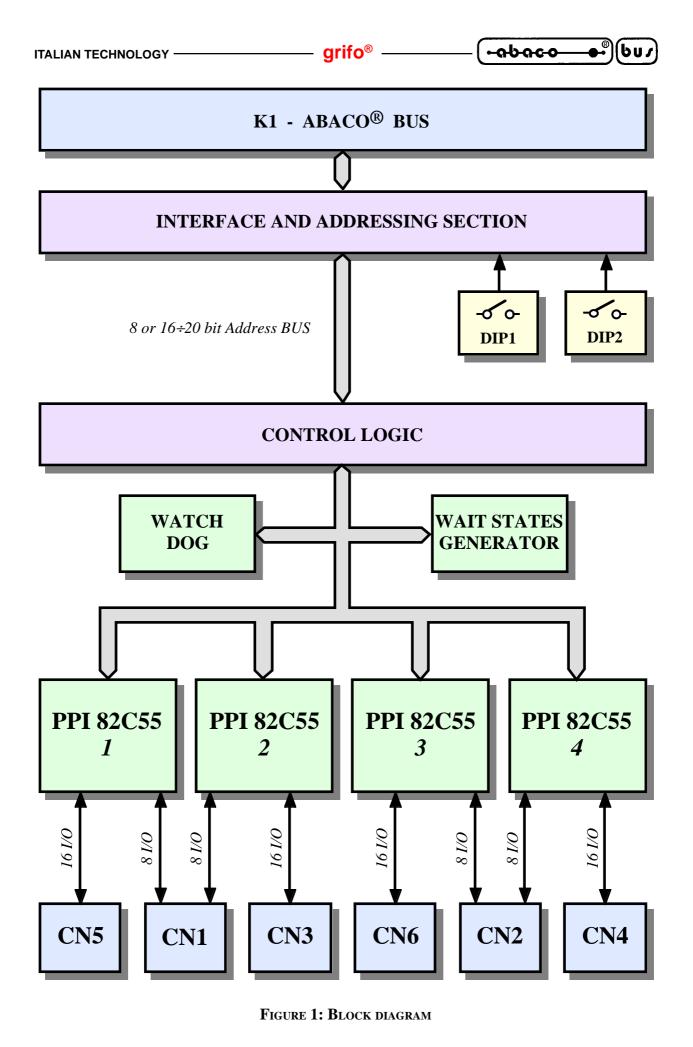

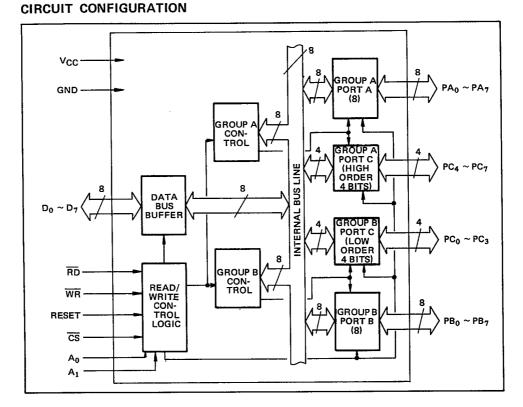

Here follows a description of the board's functional blocks, with an indication of the operations performed by each one.

To easily locate the blocks and their interconnection please refer to figure 1.

#### ADDRESSING AND INTERFACEMENT

This section manages the information interchange between control logic and external **GPC**<sup>®</sup> control cards through **ABACO**<sup>®</sup> BUS. In detail, each byte read or written passes through this section, that also provides the I/O board mapping two dip swithces called DIP1 and DIP2. Please remark that this section can be configured to address **PIO 01** in a 256 bytes or 64÷1024 Kbytes I/O addressing range. The **ABACO**<sup>®</sup> **Industrial BUS** interfacement has been designed anticipating an 8 bits data path. For further information please refer to the chapters dedicated to hardware and software description.

#### **CONTROL LOGIC**

This section generates all the chip select signals essential to access the **PIO 01** on board peripherals. It allows the programmer to reach the board devices and check their status, read the digital inputs and outputs, etc.

The control logic interfaces to **ABACO<sup>®</sup> Industrial BUS** through the addressing and interfacement section, the BUS connection allows an easy software management of all the sections. For further information please refer to the chapter dedicated to software descritption.

# WATCH DOG

**PIO 01** is provided with one sophisticated watch dog circuit that acts directly to the **ABACO**<sup>®</sup> BUS and can reset the intelligent control card at programmable time intervals, if not retriggered. Watch dog circuit is used when the user wants to exit from endless loops or to reset anomalous conditions not estimated by application program. The watch dog can be astable or monostable, with intervention time selectable between 1msec up to 16.50 sec through jumper and trimmer. By software the user can perform a complete management of the device, using specific registers. This circuitery gives to the board an extremly high degree of safety. For further information please refer to the chapters dedicated to hardware and software description.

# WAIT STATE GENERATOR

The sophisticated wait state generator installed on **PIO 01** intervents directly to **ABACO**<sup>®</sup> BUS and allows to insert a programmable number of wait states whenever **PIO 01** performs an I/O operation. A set of comfortable jumpers allow to decide the configuration of this circuitery (number of wait states and activation or deactivation).

The main purpose of this section is to allow to use **PIO 01** also matched with very fast CPU boards, and so to increase its versatility.

*Rel.* 5.00

# TTL I/O LINES

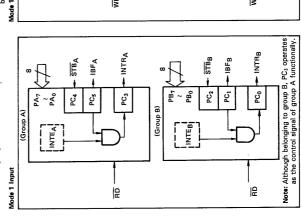

This section, based on four PPI 82C55, manages 96 TTL I/O lines divided in twelve 8 bit parallel ports. The lines direction is software settable at byte or nibble level. The software management is performed through 16 registers that control directly the four devices.

The 96 I/O lines are available on six standard **ABACO®** I/O 20 pins connectors for the direct connection to the several modules, provided with the same kind of connector, which allow to manage transistor or relay outputs, optocoupled inputs, operator interface devices like keyboards or displays, printers, etc.

The four PPI 82C55 can also be programmed to implement sophisticated parallel high speed data transfer protocols, to connect to systems provided with compatible interfaces.

For further informations about the above described device, plese refer to the manifacturer documentations or to appendix B of this manual.

| -abaco | <u> </u> | ®     | Б        | u | 2   |

|--------|----------|-------|----------|---|-----|

|        |          | • • • | <b>_</b> | • | • / |

TECHNICAL FEATURES

# **GENERAL FEATURES**

| On board resources:              | <ul> <li>96 programmable Input/Output TTL (4 PPI 82C55)</li> <li>1 Watch dog (astable or monostable)</li> <li>1 Wait state generator</li> <li>2 Dip-switches with 8 pins to set I/O address</li> </ul> |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BUS implemented:                 | ABACO <sup>®</sup> industrial<br>8 bits wide data path.                                                                                                                                                |

| Bytes of addressing space:       | Selectable between 256 bytes and 64÷1024 Kbytes                                                                                                                                                        |

| Bytes taken:                     | 16                                                                                                                                                                                                     |

| Watch dog intervent time:        | Settable between 1 msec and 16.50 sec<br>Set to about 1 sec in test phase                                                                                                                              |

| Number of wait state insertable: | Selectable amongst 3, 5 or 8                                                                                                                                                                           |

| On board peripherals:            | PPI 82C55                                                                                                                                                                                              |

**PHYSICAL FEATURES**

| Size:              | Standard EUROCARD format 100x160 mm                                                                                                                                                                                                                                    |  |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Weight:            | 160 g                                                                                                                                                                                                                                                                  |  |

| Connectors:        | K1: DIN 41612 64 pins M 90° A+C type C<br>CN1: Low profile 20 pins vertical M<br>CN2: Low profile 20 pins vertical M<br>CN3: Low profile 20 pins vertical M<br>CN4: Low profile 20 pins vertical M<br>CN5: Low profile 20 pins 90° M<br>CN6: Low profile 20 pins 90° M |  |

| Temperature range: | from 0°C to 70° C                                                                                                                                                                                                                                                      |  |

| Relative humidity: | 20% up to 90% (without condensate)                                                                                                                                                                                                                                     |  |

|                                | grifo <sup>®</sup> ———————————————————————————————————— |

|--------------------------------|---------------------------------------------------------|

| ELECTRIC FEATURES              |                                                         |

| Power supply voltage:          | $+5 \text{ Vdc} \pm 5\%$                                |

| Current consumption:           | 140 mA                                                  |

| Current for TTL lines driving: | Max 2,5 mA each line                                    |

| Voltage level of TTL lines:    | 0 V (low level); +5 Vdc (high level)                    |

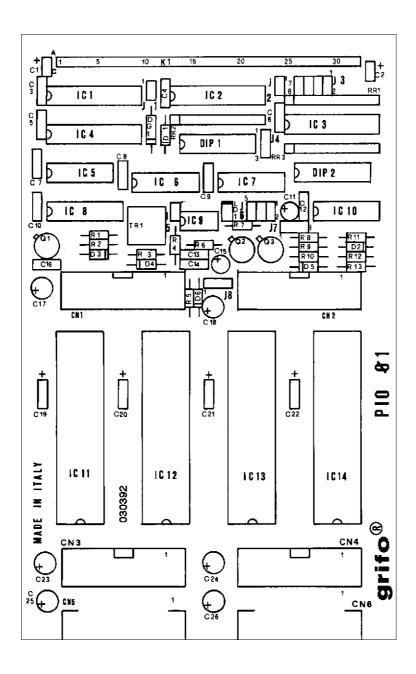

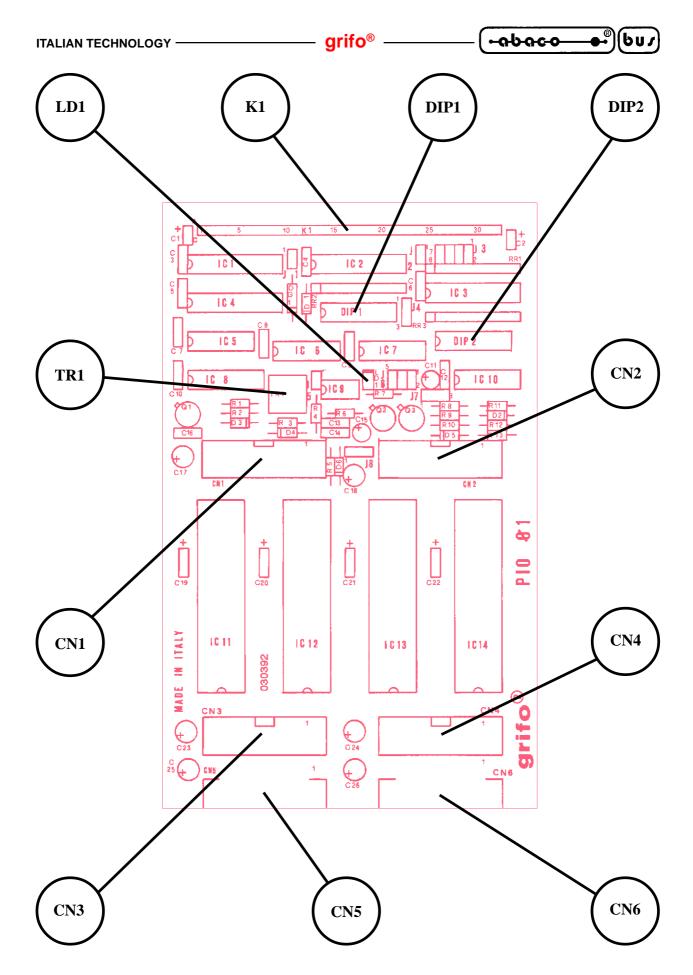

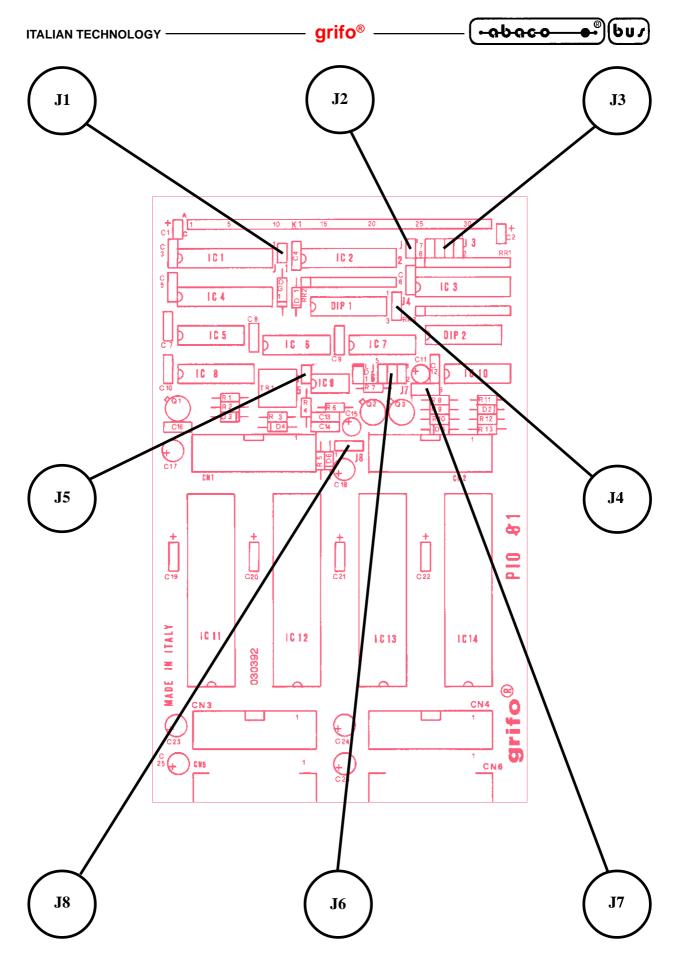

FIGURE 2: COMPONENTS MAP

#### INSTALLATION

In this chapter there are the information for a right installation and correct use of the board. The user can find the location and functions of each connectors, trimmers, jumpers and some explanatory diagrams.

grifo®

#### **CONNECTIONS**

The board has seven connectors that can be linkeded to other devices or directly to the field, according to system requirements. In this paragraph there are connectors pin outs, a short signals description (including the signals direction) and connectors location, plus some figures that describe how the interface signals are connected on the card.

To easily locate the connectors please refer to figure 6.

#### CN1 - PORT B OF PPI 82C55 SECTIONS 1 AND 2 CONNECTOR

CN1 is a 20 pins low profile vertical male 2.54 mm pitch connector.

On connector CN1 are available the 16 I/O digital lines managed through port B of PPI 82C55 belonging to sections 1 and 2. Any parameter of this device (like signals direction, data management mode, etc.) is completely software definible by programming the device itself. All signals are at TTL level and follow the standard I/O **ABACO**<sup>®</sup> pin-out.

|                   | r                 |                    |                                    |

|-------------------|-------------------|--------------------|------------------------------------|

| <u>PPI 1 PB.1</u> | -10               | 2<br><b>o</b>      | PP <u>I</u> 1 <u>P</u> B <u>.0</u> |

| <u>PPI 1 PB.3</u> | $-\frac{3}{0}$    | 4<br>o             | PPI1_PB.2                          |

| <u>PPI_1 PB.5</u> | <b>5</b>          | 6<br>0             | PP <u>I</u> 1 <u>P</u> B <u>.4</u> |

| <u>PPI_1 PB.7</u> | <b>7</b>          | 8<br><b>o</b> – -  | PP <u>I</u> 1 <u>P</u> B. <u>6</u> |

| <u>PPI 2 PB.6</u> | -]-0              | 10<br><b>o</b>     | PPI 2 PB.7                         |

| <u>PPI 2 PB.4</u> | -11<br>-0         | 12<br><b>o</b>     | <u>PPI 2 PB.5</u>                  |

| <u>PPI_2 PB.2</u> |                   | 14<br><b>o</b>     | PP <u>I 2 P</u> B. <u>3</u>        |

| <u>PPI 2 PB.0</u> | 15<br>- <b>0</b>  | 16<br><b>0</b>     | PPI 2 PB.1                         |

| <u>GND</u>        | -17<br>- <b>0</b> | 18<br><b>0</b> – - | +5_Vdc                             |

| <u>GND</u>        | <b>0</b>          | 20<br><b>o</b>     | <u> </u>                           |

|                   |                   |                    |                                    |

FIGURE 3: CN1 - PORT B OF PPI 82C55 SECTIONS 1 AND 2 CONNECTOR

Signals description:

| PPI 1 PB.n | = I/O - n-th digital TTL signal of section 1 PPI 82C55 port B |

|------------|---------------------------------------------------------------|

| PPI 2 PB.n | = I/O - n-th digital TTL signal of section 2 PPI 82C55 port B |

| +5 Vdc     | = O $-+5$ Vdc power supply                                    |

| GND        | = - Digital ground                                            |

| N.C.       | = - Not connected                                             |

—— grifo<sup>®</sup> –

●®`

)(bu*x*)

#### CN5 - PORTS A AND C OF PPI 82C55 SECTION 1 CONNECTOR

CN5 is a 20 pins low profile 90° male 2.54 mm pitch connector.

On connector CN5 are available the 16 I/O digital lines managed through port A and C of PPI 82C55 belonging to section 1. Any parameter of this device (like signals direction, data management mode, etc.) is completely software definible by programming the device itself. All signals are at TTL level and follow the standard I/O **ABACO**<sup>®</sup> pin-out.

|                   | r                 |                    |                                    |

|-------------------|-------------------|--------------------|------------------------------------|

| <u>PPI_1 PA.1</u> | -1<br>-0          | 2<br><b>o</b>      | PP <u>I</u> 1 <u>P</u> A.0         |

| <u>PPI1PA.3</u>   | $-\frac{3}{0}$    | 4<br>o             | <u>PPI 1 PA.2</u>                  |

| <u>PPI1PA.5</u>   | $-\frac{5}{0}$    | 6<br>0             | PP <u>I</u> 1 <u>P</u> A <u>.4</u> |

| <u>PPI 1 PA.7</u> | <mark>7</mark>    | 8<br>0             | PP <u>I</u> 1 <u>P</u> A. <u>6</u> |

| PPI 1 PC.6        | -]-8              | 10<br><b>o</b>     | PPI1_PC.7                          |

| <u>PPI 1 PC.4</u> | -11<br>-0         | 12<br><b>o</b>     | <u>PPI 1 PC.5</u>                  |

| <u>PPI_1 PC.2</u> |                   | 14<br>o            | <u>PPI1PC.3</u>                    |

| <u>PPI 1 PC.0</u> | -15<br>- <b>0</b> | 16<br><b>0</b>     | PPI1PC.1                           |

| <u>GND</u>        | -17<br>- <b>0</b> | 18<br><b>0</b> – - | +5_Vdc                             |

| <u>GND</u>        | <b>1</b> 9        | 20<br><b>o</b>     | <u> </u>                           |

|                   |                   |                    |                                    |

FIGURE 5: CN5 - PORTS A AND C OF PPI 82C55 SECTION 1 CONNECTOR

| PPI 1 PA.n | = I/O - n-th digital TTL signal of section 1 PPI 82C55 port A |

|------------|---------------------------------------------------------------|

| PPI 1 PC.n | = I/O - n-th digital TTL signal of section 1 PPI 82C55 port C |

| +5 Vdc     | = O - +5 Vdc power supply                                     |

| GND        | <ul> <li>– Digital ground</li> </ul>                          |

| N.C.       | = - Not connected                                             |

FIGURE 6: CONNECTORS, DIP SWITCHES, LED AND TRIMMER LOCATIONS

#### CN3 - PORTS A AND C OF PPI 82C55 SECTION 2 CONNECTOR

CN3 is a 20 pins low profile 90° male 2.54 mm pitch connector.

On connector CN3 are available the 16 I/O digital lines managed through port A and C of PPI 82C55 belonging to section 2. Any parameter of this device (like signals direction, data management mode, etc.) is completely software definible by programming the device itself. All signals are at TTL level and follow the standard I/O **ABACO**<sup>®</sup> pin-out.

|                   | r                  |                    |                   |

|-------------------|--------------------|--------------------|-------------------|

| <u>PPI 2 PA.1</u> | -1<br>-0           | 2<br><b>o</b>      | PPI 2 PA.0        |

| <u>PPI 2 PA.3</u> | $-\frac{3}{0}$     | 4<br>0             | <u>PPI 2 PA.2</u> |

| <u>PPI 2 PA.5</u> | $-\frac{5}{0}$     | 6<br>0             | <u>PPI 2 PA.4</u> |

| <u>PPI 2 PA.7</u> | $-\frac{7}{2}$     | 8<br><b>o</b>      | <u>PPI2PA.6</u>   |

| <u>PPI 2 PC.6</u> | 8                  | 10<br><b>O</b>     | <u>PPI 2 PC.7</u> |

| <u>PPI 2 PC.4</u> | - 11<br>- <b>0</b> | 12<br><b>o</b>     | <u>PPI 2 PC.5</u> |

| <u>PPI2PC.2</u>   |                    | 14<br><b>o</b>     | PPI2PC.3          |

| <u>PPI 2 PC.0</u> | $-{}^{15}_{0}$     | 16<br><b>0</b>     | <u>PPI 2 PC.1</u> |

| <u>GND</u>        | -17                | 18<br><b>0</b> – - | - $    +5Vdc$     |

| <u>GND</u>        | $-{}^{19}_{o}$     | 20<br><b>o</b>     | <u>.N.C.</u>      |

|                   |                    |                    |                   |

FIGURE 7: CN3 - PORTS A AND C OF PPI 82C55 SECTION 2 CONNECTOR

| PPI 2 PA.n<br>PPI 2 PC.n | = I/O - n-th digital TTL signal of section 2 PPI 82C55 port A<br>= I/O - n-th digital TTL signal of section 2 PPI 82C55 port C |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| +5 Vdc                   | = O - +5 Vdc power supply                                                                                                      |

| GND                      | <ul> <li>– Digital ground</li> </ul>                                                                                           |

| N.C.                     | = - Not connected                                                                                                              |

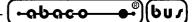

FIGURE 8: CARD PHOTO

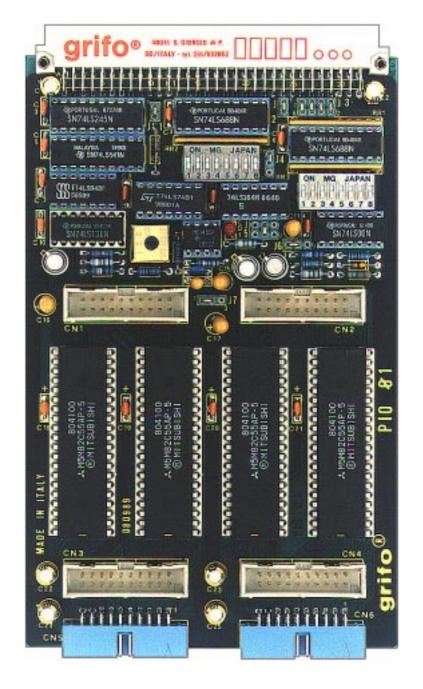

#### CN2 - PORT B OF PPI 82C55 SECTIONS 3 AND 4 CONNECTOR

CN2 is a 20 pins low profile vertical male 2.54 mm pitch connector.

On connector CN2 are available the 16 I/O digital lines managed through port B of PPI 82C55 belonging to sections 3 and 4. Any parameter of this device (like signals direction, data management mode, etc.) is completely software definible by programming the device itself. All signals are at TTL level and follow the standard I/O **ABACO**<sup>®</sup> pin-out.

| <u>PPI 3 PB.1</u> | -10               | 2<br><b>o</b>            | PPI 3 <u>P</u> B.0                 |

|-------------------|-------------------|--------------------------|------------------------------------|

| <u>PPI 3 PB.3</u> | $-\frac{3}{0}$    | <b>4</b><br><b>o</b> − − | <u>PPI 3 PB.2</u>                  |

| <u>PPI 3 PB.5</u> | $-\frac{5}{0}$    | 6<br>0                   | PP <u>I</u> 3 <u>P</u> B.4         |

| <u>PPI 3 PB.7</u> | $-\frac{7}{6}$    | 8<br><b>o</b>            | <u>PPI 3 PB.6</u>                  |

| <u>PPI 4 PB.6</u> | -]-8              | 10<br>O— -               | PPI 4 <u>P</u> B.7                 |

| <u>PPI 4 PB.4</u> | -11<br>-0         | 12<br><b>o</b>           | <u>PPI 4 PB.5</u>                  |

| <u>PPI_4 PB.2</u> | - 13<br><b>o</b>  | 14<br>o                  | PP <u>I</u> 4 <u>P</u> B. <u>3</u> |

| <u>PPI 4 PB.0</u> | -15<br>- <b>0</b> | 16<br><b>0</b> — -       | <u>PPI</u> 4 <u>P</u> B.1          |

| <u>GND</u>        | -17               | 18<br><b>0</b> – -       | +5_Vdc                             |

| <u>GND</u>        | <mark>1</mark> 9  | 20<br><b>o</b>           | <u>.</u> N. <u>C</u> .             |

|                   |                   |                          |                                    |

FIGURE 9: CN2 - PORT B OF PPI 82C55 SECTIONS 3 AND 4 CONNECTOR

| PPI 3 PB.n | = I/O - n-th digital TTL signal of section 3 PPI 82C55 port B |

|------------|---------------------------------------------------------------|

| PPI 4 PB.n | = I/O - n-th digital TTL signal of section 4 PPI 82C55 port B |

| +5 Vdc     | = O $-+5$ Vdc power supply                                    |

| GND        | <ul> <li>– Digital ground</li> </ul>                          |

| N.C.       | = - Not connected                                             |

|            |                                                               |

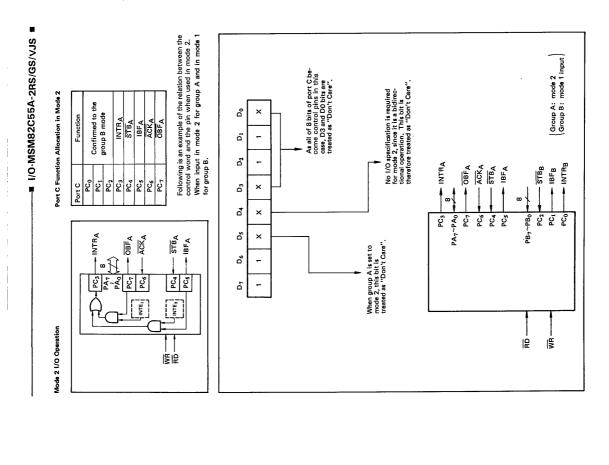

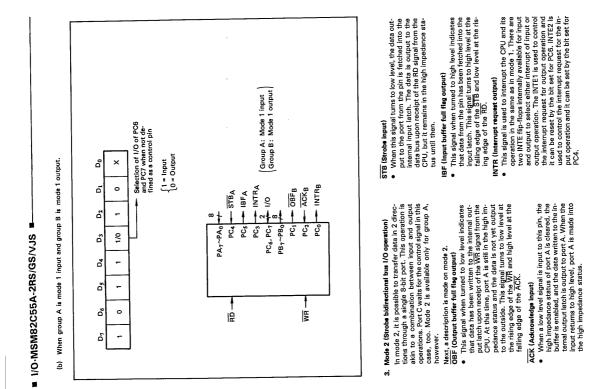

FIGURE 10: PPI 82C55 SECTIONS 3 AND 4 BLOCK DIAGRAM

#### CN6 - PORTS A AND C OF PPI 82C55 SECTION 3 CONNECTOR

CN6 is a 20 pins low profile 90° male 2.54 mm pitch connector.

On connector CN6 are available the 16 I/O digital lines managed through port A and C of PPI 82C55 belonging to section 3. Any parameter of this device (like signals direction, data management mode, etc.) is completely software definible by programming the device itself. All signals are at TTL level and follow the standard I/O **ABACO**<sup>®</sup> pin-out.

| <u>PPI 3 PA.1</u> | $-^{1}_{0}$       | 2<br><b>o</b>      | PPI 3 <u>P</u> A.0 |

|-------------------|-------------------|--------------------|--------------------|

| PPI 3 PA.3        | $-\frac{3}{0}$    | 4<br><b>o</b>      | PPI 3 PA.2         |

| <u>PPI 3 PA.5</u> | <b>5</b>          | 6<br>0             | <u>PPI 3 PA.4</u>  |

| <u>PPI 3 PA.7</u> | $-\frac{7}{2}$    | 8<br><b>o</b>      | <u>PPI 3 PA.6</u>  |

| PPI 3 PC.6        | 8                 | 10<br><b>o</b>     | PPI 3 PC.7         |

| <u>PPI 3 PC.4</u> | - 11<br>- 0       | 12<br><b>o</b>     | PPI3PC.5           |

| <u>PPI 3 PC.2</u> | 13<br>0           | 14<br>o            | PP <u>13PC.3</u>   |

| <u>PPI 3 PC.0</u> | -15<br>- <b>0</b> | 16<br><b>0</b>     | PPI3PC.1           |

| <u>GND</u>        | -17<br>- <b>0</b> | 18<br><b>0</b> – - | +5_Vdc             |

| <u>GND</u>        | <mark>1</mark> 9  | 20<br><b>o</b>     | <u>N.C.</u>        |

|                   |                   |                    |                    |

FIGURE 11: CN6 - PORTS A AND C OF PPI 82C55 SECTION 3 CONNECTOR

| PPI 3 PA.n | = I/O - n-th digital TTL signal of section 3 PPI 82C55 port A |

|------------|---------------------------------------------------------------|

| PPI 3 PC.n | = I/O - n-th digital TTL signal of section 3 PPI 82C55 port C |

| +5 Vdc     | = O + 5 Vdc power supply                                      |

| GND        | = - Digital ground                                            |

| N.C.       | = - Not connected                                             |

#### CN4 - PORTS A AND C OF PPI 82C55 SECTION 4 CONNECTOR

CN4 is a 20 pins low profile vertical male 2.54 mm pitch connector.

On connector CN4 are available the 16 I/O digital lines managed through port A and C of PPI 82C55 belonging to section 4. Any parameter of this device (like signals direction, data management mode, etc.) is completely software definible by programming the device itself. All signals are at TTL level and follow the standard I/O **ABACO**<sup>®</sup> pin-out.

| <u>PPI 4 PA.1</u> | $-^{1}_{0}$        | 2<br><b>o</b>            | PP <u>I</u> 4 <u>P</u> A.0         |

|-------------------|--------------------|--------------------------|------------------------------------|

| <u>PPI 4 PA.3</u> | $-\frac{3}{0}$     | <b>4</b><br><b>o</b> − - | <u>PPI 4 PA.2</u>                  |

| <u>PPI_4 PA.5</u> | $-\frac{5}{0}$     | 6<br>0                   | PP <u>I</u> 4 <u>P</u> A <u>.4</u> |

| <u>PPI4PA.7</u>   | $-\frac{7}{6}$     | 8<br><b>o</b>            | PPI4 <u>P</u> A.6                  |

| <u>PPI 4 PC.6</u> | 8                  | 10<br><b>o</b>           | PPI 4 PC.7                         |

| <u>PPI 4 PC.4</u> | - 11<br>- <b>o</b> | 12<br><b>o</b>           | PPI4PC.5                           |

| <u>PPI4PC.2</u>   |                    | 14<br><b>o</b>           | <u>_PPI4PC.3</u>                   |

| <u>PPI 4 PC.0</u> | $-{}^{15}_{0}$     | 16<br><b>0</b>           | PPI4PC.1                           |

| <u>GND</u>        | -17                | 18<br><b>0</b> – -       | + <u>5 Vdc</u>                     |

| <u>GND</u>        | -19<br>- <b>o</b>  | 20<br><b>o</b>           | <u>.</u> N.C.                      |

|                   |                    |                          |                                    |

FIGURE 12: CN4 - PORTS A AND C OF PPI 82C55 SECTION 4 CONNECTOR

| PPI 4 PA.n | = I/O - n-th digital TTL signal of section 4 PPI 82C55 port A |

|------------|---------------------------------------------------------------|

| PPI 4 PC.n | = I/O - n-th digital TTL signal of section 4 PPI 82C55 port C |

| +5 Vdc     | = O + 5 Vdc power supply                                      |

| GND        | <ul> <li>– Digital ground</li> </ul>                          |

| N.C.       | = - Not connected                                             |

K1 is a 64 pins, male, 90°, DIN 41612 connector with 2.54 pitch.

On K1 are available all the industrial **ABACO**<sup>®</sup> BUS signals and it can be used for connections to many other peripheral cards. In the table below there are the standard pin outs both for 8 bits and 16 bits CPU and the signal connected on **PIO 01**. All signals, except power supplies, are compliant to TTL standard.

| Α          | Α         | Α       | PIN | С       | С         | С          |

|------------|-----------|---------|-----|---------|-----------|------------|

| 16 bit BUS | 8 bit BUS | GPC 150 |     | GPC 150 | 8 bit BUS | 16 bit BUS |

| GND        | GND       | GND     | 1   | GND     | GND       | GND        |

| +5 Vdc     | +5 Vdc    | +5 Vdc  | 2   | +5 Vdc  | +5 Vdc    | +5 Vdc     |

| D0         | D0        | D0      | 3   | N.C.    |           | D8         |

| D1         | D1        | D1      | 4   | N.C.    |           | D9         |

| D2         | D2        | D2      | 5   | N.C.    |           | D10        |

| D3         | D3        | D3      | 6   | /INT    | /INT      | /INT       |

| D4         | D4        | D4      | 7   | /NMI    | /NMI      | /NMI       |

| D5         | D5        | D5      | 8   | N.C.    | /HALT     | D11        |

| D6         | D6        | D6      | 9   | N.C.    | /MREQ     | /MREQ      |

| D7         | D7        | D7      | 10  | /IORQ   | /IORQ     | /IORQ      |

| A0         | A0        | A0      | 11  | /RD     | /RD       | /RDLDS     |

| A1         | A1        | A1      | 12  | /WR     | /WR       | /WRLDS     |

| A2         | A2        | A2      | 13  | N.C.    | /BUSAK    | D12        |

| A3         | A3        | A3      | 14  | N.C.    | /WAIT     | /WAIT      |

| A4         | A4        | A4      | 15  | N.C.    | /BUSRQ    | D13        |

| A5         | A5        | A5      | 16  | /RESET  | /RESET    | /RESET     |

| A6         | A6        | A6      | 17  | N.C.    | /M1       | /IACK      |

| A7         | A7        | A7      | 18  | N.C.    | /RFSH     | D14        |

| A8         | A8        | N.C.    | 19  | N.C.    | /MEMDIS   | /MEMDIS    |

| A9         | A9        | N.C.    | 20  | N.C.    | VDUSEL    | A22        |

| A10        | A10       | N.C.    | 21  | N.C.    | /IEI      | D15        |

| A11        | A11       | N.C.    | 22  | N.C.    |           |            |

| A12        | A12       | N.C.    | 23  | N.C.    | CLK       | CLK        |

| A13        | A13       | N.C.    | 24  | N.C.    |           | /RDUDS     |

| A14        | A14       | N.C.    | 25  | N.C.    |           | /WRUDS     |

| A15        | A15       | N.C.    | 26  | N.C.    |           | A21        |

| A16        |           | N.C.    | 27  | N.C.    |           | A20        |

| A17        |           | N.C.    | 28  | N.C.    |           | A19        |

| A18        |           | N.C.    | 29  | /R.T.   | /R.T.     | /R.T.      |

| +12 Vdc    | +12 Vdc   | N.C.    | 30  | N.C.    | -12 Vdc   | -12 Vdc    |

| +5 Vdc     | +5 Vdc    | +5 Vdc  | 31  | +5 Vdc  | +5 Vdc    | +5 Vdc     |

| GND        | GND       | GND     | 32  | GND     | GND       | GND        |

FIGURE 13: K1 - ABACO® BUS CONNECTOR

PIO 01

ITALIAN TECHNOLOGY \_\_\_\_\_ grifo<sup>®</sup> -

Signals description:

8 bits CPU

| Address BUS             |

|-------------------------|

| Data BUS                |

|                         |

| nterrupt request        |

| Non Maskable Interrupt  |

| Halt state              |

| Aemory Request          |

| nput Output Request     |

| Read cycle status       |

| Vrite cycle status      |

| BUS Acknowledge         |

| Vait                    |

| BUS Request             |

| Reset                   |

| Aachine cycle one       |

| Refresh for dynamic RAM |

| Memory Display          |

| DU Selection            |

| nterrupt Enable Input   |

| system clock            |

| Reset button            |

| Power supply at +5 Vdc  |

| Power supply at +12 Vdc |

| Power supply at -12 Vdc |

| Bround signal           |

|                         |

16 bits CPU

| A16-A22       | = | Ο   | - Address BUS             |

|---------------|---|-----|---------------------------|

| D8-D15        | = | I/O | - Data BUS                |

| <b>RD UDS</b> | = | 0   | - Read Upper Data Strobe  |

| WR UDS        | = | Ο   | - Write Upper Data Strobe |

| IACK          | = | Ο   | - Interrupt Acknowledge   |

| <b>RD LDS</b> | = | 0   | - Read Lower Data Strobe  |

| WR LDS        | = | Ο   | - Write Lower Data Strobe |

#### NOTE

Directionality indications as above stated are referred to a master (GPC®) board and have been kept untouched to avoid ambiguity in case of multi-boards systems.

#### VISUAL FEEDBACK

**PIO 01** board is provided with one LED to signal status conditions, as described in the following table:

| LED | COLOUR | FUNCTION                                       |

|-----|--------|------------------------------------------------|

| LD1 | Red    | Indicates the watch dog circuitery activation. |

#### FIGURE 14: VISUAL FEEDBACK TABLE

The main purpose of this LED is to give a visual indication of the board status, making easier the operations of system working verify. To easily locate this LED on the board, please refer to figure 6.

#### **POWER SUPPLY**

**PIO 01** is provided with an efficient circuitery that solves in a comfortable and simple way the problem of the board's supply, under any condition of use. Here follow the voltages nedded:

+5 Vdc: Supplies the on board logic; must be in the range +5 Vdc  $\pm$  5% and must be provided through the specific pins of connector K1 (ABACO<sup>®</sup> BUS).

To warrant great immunity to external noise and so a correct working of the board, it is essential that +**5Vdc** tension is galvanically isolated from any other supply tensions available in the system.

#### **BOARD CONNNECTIONS**

To prevent possible connecting problems between **PIO 01** board and the external systems, the user has to read carefully the information of the previous paragraphs and he must follow these instrunctions:

- The TTL signals can be connected directly only to a device featuring the same type of interface. About the correspondance between logic signals and TTL output status, remember that a logic **0** generates a TTL 0 Vdc, while a logic **1** generates a TTL +5 Vdc.

#### **RESET CIRCUITRY**

**PIO 01** features an efficent reset circuitery that, whenever a reset signal comes from **ABACO**<sup>®</sup> BUS or a Power On occours, resets all the 96 I/O signals to their initial status, that is all the signals are configured as inputs.

This is done to avoid random settings and/or undesired variations of the outputs and to warrant a safe status of the signals during this critical phase.

**ITALIAN TECHNOLOGY** -

# grifo<sup>®</sup> ———

# JUMPERS

On **PIO 01** there are 8 jumpers for card configuration. Connecting these jumpers, the user can define the board working parameters, the peripheral devices functionality and so on. Below there is the jumpers list, location and function:

| JUMPERS | N. PINS | PURPOSE                                                                                                             |

|---------|---------|---------------------------------------------------------------------------------------------------------------------|

| J1      | 2       | Selects the connection of the /WAIT signal, generated by the on board circuitery, to <b>ABACO</b> <sup>®</sup> BUS. |

| J2      | 2       | Selects the connection of the /M1 signal, from <b>ABACO</b> <sup>®</sup> BUS, to the on board circutery.            |

| J3      | 8       | Defines the addressing space for extended addressing mode, between 64 Kbytes and 1 Mbytes.                          |

| J4      | 3       | Selects between normal 256 bytes addressing mode and extended 64÷1024 Kbytes addressing mode.                       |

| J5      | 2       | Selects the watch dog working mode.                                                                                 |

| J6      | 6       | Selects the number of wait states generated by the proper circuitery.                                               |

| J7      | 3       | Selects the connection of the /R.T. signal, generated by the on boardwatch dog, to $ABACO^{\textcircled{B}}$ BUS.   |

| J8      | 3       | Defines the watch dog intervent time.                                                                               |

# FIGURE 15: JUMPERS SUMMARIZING TABLE

The following tables describe all the right connections of **PIO 01** jumpers with their relative functions. To recognize these valid connections, please refer to the board printed diagram (serigraph) or to figure 2 of this manual, where the pins numeration is listed; for recognizing jumpers location, please refer to figure 19.

The "\*" used in the following tables, denotes the default connection, or on the other hand the connection set up at the end of testing phase, that is the configuration the User receives.

# 6 PINS JUMPER

| JUMPER | CONNECTION   | PURPOSE                                                                   | DEF. |

|--------|--------------|---------------------------------------------------------------------------|------|

|        |              | Configures the board for introducing 3 Wait states in the I/O operations. | *    |

| J6     | position 3-4 | Configures the board for introducing 5 Wait states in the I/O operations. |      |

|        | position 5-6 | Configures the board for introducing 8 Wait states in the I/O operations. |      |

# FIGURE 16: 6 PINS JUMPERS TABLE

| PIO 01 | Rel. 5.00 – | <b>`</b> |  |

|--------|-------------|----------|--|

|--------|-------------|----------|--|

| (-abac-o_●•)(bu/) | – grifo <sup>®</sup> ——— | ITALIAN TECHNOLOGY |

|-------------------|--------------------------|--------------------|

|-------------------|--------------------------|--------------------|

# 2 PINS JUMPERS

| JUMPER | CONNECTION    | PURPOSE                                                                                                                           | DEF. |

|--------|---------------|-----------------------------------------------------------------------------------------------------------------------------------|------|

| J1     | not connected | It does not connect the /WAIT signal generated by the on board circuitery to <b>ABACO</b> <sup>®</sup> BUS.                       | *    |

| 51     | connected     | It connects the /WAIT signal generated by the on board circuitery to <b>ABACO</b> <sup>®</sup> BUS.                               |      |

| J2     | not connected | The interfacement and addressing section does not take care of managing the /M1 signal coming from <b>ABACO</b> <sup>®</sup> BUS. |      |

| J2     | connected     | The interfacement and addressing section takes care of managing the /M1 signal that is coming from <b>ABACO</b> <sup>®</sup> BUS. | *    |

| J5     | not connected | Selects monostable working mode for on board watch dog circuitery.                                                                |      |

| 10     | connected     | Selects astable working mode for on board watch dog circuitery.                                                                   | *    |

# FIGURE 17: 2 PINS JUMPERS TABLE

#### **3 PINS JUMPERS**

| JUMPER     | CONNECTION    | PURPOSE                                                                                               | DEF. |

|------------|---------------|-------------------------------------------------------------------------------------------------------|------|

| IA         | position 1-2  | It selects 256 bytes normal addressing mode.                                                          | *    |

| J4         | position 2-3  | It selects 64÷1024 Kbytes extended addressing mode.                                                   |      |

| 17         | position 1-2  | It connects the output of watch dog circuitery to pin /R.T. of <b>ABACO</b> <sup>®</sup> BUS.         |      |

| J7         | position 2-3  | It does not connect the output of watch dog circuitery to pin /R.T. of <b>ABACO</b> <sup>®</sup> BUS. |      |

|            | not connected | It selects low intervent time (1÷72 msec) for on board watch dog circuitery.                          |      |

| <b>J</b> 8 | position 1-2  | It selects average intervent time (30 msec÷1,76 sec) for on board watch dog circuitery.               |      |

|            | position 2-3  | It selects long intervent time (295 msec÷16,50 sec) for on board watch dog circuitery.                |      |

FIGURE 18: 3 PINS JUMPERS TABLE

\_

FIGURE 19: JUMPERS LOCATION

<del>abaco</del> bus

#### **8 PINS JUMPERS**

| JUMPER | CONNECTION                            | PURPOSE                                                                                                                                                                                  | DEF. |

|--------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|        | not connected                         | If normal addressing mode has been seleced, then this jumper <u>must be</u> in this position.<br>If extended addressing mode has been seleced, it defines 64 Kbytes of addressing space. | *    |

|        | position 7-8                          | If extended addressing mode has been seleced, it defines 128 Kbytes of addressing space, connecting also address signal A16 to the proper circuitery.                                    |      |

| J3     | positions<br>5-6 and 7-8              | If extended addressing mode has been seleced, it defines 256 Kbytes of addressing space, connecting also address signals A16 and A17 to the proper circuitery.                           |      |

|        | positions<br>3-4, 5-6 and 7-8         | If extended addressing mode has been seleced, it defines 512 Kbytes of addressing space, connecting also address signals A16, A17 and A18 to the proper circuitery.                      |      |

|        | positions<br>1-2, 3-4, 5-6 and<br>7-8 | If extended addressing mode has been seleced, it defines 1 Mbytes of addressing space, connecting also address signals A16, A17, A18 and A19 to the proper circuitery.                   |      |

FIGURE 20: 8 PINS JUMPERS TABLE

# **WAIT STATE GENERATOR**

**PIO 01** board is provided with a sophisticated Wait State generator designed to act directly to **ABACO<sup>®</sup>** BUS and, if enabled, capable to insert a configurable number of wait states in the I/O operations of **PIO 01** board.

The previously described jumper J6 is used to set the number of wait states to introduce (3, 5 or 8); while jumper J1 allows to enable the circuitery by connecting its output to the /WAIT signal of **ABACO**<sup>®</sup> BUS.

To easily locate the aboce mentioned components, please refer to figure 19.

# NOTE

The correct working of on board wait state generator depends on the presence of CLK singnal from **ABACO®** BUS. Please refer to the technical manual of the intelligent control card being used (**GPC®** serie) to chek its effective presence.

For further information please contact **grifo**<sup>®</sup> directly.

*Rel.* 5.00

#### **grifo**<sup>®</sup>

#### **RESET AND WATCH DOG**

**PIO 01** is provided with one Watch Dog circuitery that is really efficient and easy to use. The most important features of the Watch Dog circuitery are:

- astable or monostable mode;

- intervention time settable from 1 msec to 16.50 sec (modificable by hardware);

- enable function by hardware;

- retrigger by software;

Watch Dog intervent is signaled by the lighting of LED LD1. The previously described jumper **J5** selects the working modality of the circuitery:

Monostable:In monostable mode when intervention time is elapsed the circuit becomes<br/>active and it stays active as far as a reset or power on occour.Astable:In astable mode when intervention time is elapsed the circuit becomes<br/>active, it stays active for about 8 msec then it is again deactivated.

Jumper J7 selects whether to connect or not the output of this circuitery to the signal /R.T. of ABACO<sup>®</sup> BUS. This would cause the following events:

- Intervent of **PIO 01** watch dog circuitery.

- Activation of signal /R.T. of ABACO® BUS (reset request).

- Activation of reset circuitery on GPC® serie intelligent control card.

- Activation of /RESET signal of ABACO® BUS by control card.

- Overall system reset.

Intervent time can be set through jumper **J8** and trimmer **TR1**; table in figure 18 shows the jumper connections to set short, average or long time interval; setting the exact intervent time within the selected interval is done through trimmer **TR1**.

Please remark that default setting for these components, that is the intervent time set during the test phase of production, is about **1 sec**.

About retrigger operation of internal and external watch dog circuits, please refer to paragraph "WATCH DOG" in chapter "PERIPHERAL DEVICES SOFTWARE DESCRIPTION".

To easily locate the above mentioned components please refer to figures 6 and 19, in the previous pages.

#### NOTE

The correct working of on board watch dog circuitery depends on the presence of CLK signal from **ABACO®** BUS. Please refer to the technical manual of the control card being used (**GPC®** serie) to chek its effective presence.

For further information please contact **grifo**<sup>®</sup> directly.

# **DIGITAL I/O INTERFACES**

Through CN3, CN4, CN5 and CN6 (**I/O Abaco**<sup>®</sup> standard connector) the **PIO 01** card can be connected to all of the numerous **grifo**<sup>®</sup> boards featuring the same standard pin out. Installation of these interface is very easy; in fact only a 20 pins flat cable (code **FLT.20+20**) is required, while the software management of these interfaces is as easy; in fact most of the software packages available for **PIO 01** card are provided with the necessary procedures. Remarkable modules are:

- QTP 16P, QTP 24P, KDL x24, KDF 224, DEB 01, etc. that solve all the local operator interfacing problems. These modules are provided with all the resources needed to obtain a high-level human-machine interface (they feature alphanumeric displays, matrix keyboard and visualization LEDs) at a short distance from PIO 01 card. The available software drivers allow to manage the operator interface resources directly through the high-level instructions for console management. These procedures are software features added to the ones the language already provides and allow to drive the operatore interface directly through instructions like PRINT and INPUT in BASIC or PRINTF and SCANF in C. This drastcally simplifies the write operations to the display and the input operations from the keyboard.

- IAC 01, DEB 01: it is an interface for CENTRONICS parallel printer that can be connected with a standard printer cable. The printer is managed by software through the high level instructions of the selected programming language (LPRINT for BASIC, PRINTF for C, etc.).

- MCI 64: it a large mass memory support that can directly manage the PCMCIA memory cards RAM, FLASH, ROM, etc.) in their available sizes. About software the developed drivers provide a complete file system interfacing allowing to access the informations stored in the memory carddirectly through the high-level file management instructions.

- **RBO xx**, **TBO xx**, **XBI xx**, **OBI xx**: these are buffer interfaces for I/O TTL signals. With these modules the the TTL input signals are converted in NPN or PNP optoisolated inputs and the TTL output signals are converted in relays or transistor optoisolated outputs. Some of the above mentioned interfaces can be connected directly to CN4.

$For more information \ refer to \ "EXTERNAL \ CARDS" \ chapter \ and \ the \ software \ tools \ documentation.$

HARDWARE DESCRIPTION

This chapter provides all the hardware informations needed to use **PIO 01** board. Here the user will find informations about I/O card mapping and on board peripheral devices addressing.

#### **BOARD MAPPING**

**PIO 01** board is mapped into a **16** consecutive bytes I/O addressing space that can be based starting from different base addresses according to how the board is configured. This feature allows to use several **PIO 01** cards on the same **ABACO**<sup>®</sup> BUS, or to install them on a BUS where other peripheral modules are installed obtaining a structure that can be expanded without any difficulty or modifications to the application software.

The base address can be defined through the specific BUS interface circuitry on the board itself; this circuitry uses two dip switches, both featuring 8 pins, called DIP1 and DIP2, from which it reads the address set by the user. Here follows the corrispondance between dip switches configuration and address signals.

<u>Normal addressing (**J4** in 1-2)</u>

Extended addressing (J4 in 2-3)

|               |    |                          | <i>.</i> |                        |

|---------------|----|--------------------------|----------|------------------------|

| <b>DIP2.1</b> | -> | OFF                      | (*)      | Address BUS signal A16 |

| <b>DIP2.2</b> | -> | OFF                      | (*)      | Address BUS signal A17 |

| <b>DIP2.3</b> | -> | OFF                      | (*)      | Address BUS signal A18 |

| <b>DIP2.4</b> | -> | OFF                      | (*)      | Address BUS signal A19 |

| <b>DIP2.5</b> | -> | Address BUS signal A4    |          | Address BUS signal A4  |

| <b>DIP2.6</b> | -> | Address BUS signal A5    |          | Address BUS signal A5  |

| <b>DIP2.7</b> | -> | Address BUS signal A6    |          | Address BUS signal A6  |

| <b>DIP2.8</b> | -> | Address BUS signal A7    |          | Address BUS signal A7  |

|               |    |                          |          |                        |

| <b>DIP1.1</b> | -> | Don't care               |          | Address BUS signal A8  |

| <b>DIP1.2</b> | -> | Don't care               |          | Address BUS signal A9  |

| <b>DIP1.3</b> | -> | Don't care               |          | Address BUS signal A10 |

| DIP1.4        | -> | Don't care               |          | Address BUS signal A11 |

| <b>DIP1.5</b> | -> | Don't care               |          | Address BUS signal A12 |

| <b>DIP1.6</b> | -> | Don't care               |          | Address BUS signal A13 |

|               |    |                          |          | U                      |

| DIP1.7        | -> | Don't care               |          | Address BUS signal A14 |

|               |    | Don't care<br>Don't care |          | U                      |

These dip switches are driven in complemented logic, this means that if a switch is **ON** it generates a **logic zero**, viceversa if a switch is **OFF** it generates a **logic one**.

Previously described jumper **J4** selects the range of addressing space where the base address of the board can be selected.

If a 256 bytes addressing space (from 00H to FFH) is selected, then only DIP2 is used to allocate the board (the first 4 switches <u>must be OFF</u>) while DIP1 is indifferent.

When normal addressing mode is selected, jumper J3 must be not connected.

When extended addressing mode (64÷1024 Kbytes) is selected, both DIP1 and DIP2 must be set correctly.

Jumper J3 affects the total amount of addressing space bytes, so only dip switches whose address

PIO 01 Rel. 5.00

signal is connected to the addressing circuitery, amongst the ones indicated by (\*), must be set (refer to table in figure 20); viceversa the unused switches <u>must be OFF</u>.

Please remark that jumper J2 affects the addressing section and must be set according to the type of master control board (GPC<sup>®</sup>) used to drive the PIO 01. In detail if the master control board is provided with signal /M1 on ABACO<sup>®</sup> BUS connector, then jumper J2 must be connected and viceversa.

#### NOTE

If using several boards on the same **ABACO**<sup>®</sup> BUS, when setting the boards mapping address the user shold be careful not to allocate more than one board in the same addressing space (consider the base address plus the bytes taken by the board addressing). If this condition is not satisfied a BUS conflict situation will occour, prejudicing the correct working of the whole system.

To ease the board use here follow some examples of mapping.

| 1) | Address where mapping <b>PIO 01</b> :<br>Control card used: |    |        | 1490H in a 64 Kbytes addressing space.<br>16 bits address bus;<br>not provided with signal /M1. |  |  |

|----|-------------------------------------------------------------|----|--------|-------------------------------------------------------------------------------------------------|--|--|

|    | J2                                                          | -> | Not co | onnected                                                                                        |  |  |

|    | J3                                                          | -> | Not co | Not connected                                                                                   |  |  |

|    | J4                                                          | -> | 2-3    |                                                                                                 |  |  |

|    | DIP2.1                                                      | -> | OFF    | because address A16 is not connected through J3                                                 |  |  |

|    | DIP2.2                                                      | -> | OFF    | because address A17 is not connected through J3                                                 |  |  |

|    | DIP2.3                                                      | -> | OFF    | because address A18 is not connected through J3                                                 |  |  |

|    | DIP2.4                                                      | -> | OFF    | because address A19 is not connected through J3                                                 |  |  |

|    | DIP2.5                                                      | -> | OFF    |                                                                                                 |  |  |

|    | DIP2.6                                                      | -> | ON     |                                                                                                 |  |  |

|    | DIP2.7                                                      | -> | ON     |                                                                                                 |  |  |

|    | DIP2.8                                                      | -> | OFF    |                                                                                                 |  |  |

|    | DIP1.1                                                      | -> | ON     |                                                                                                 |  |  |

|    | DIP1.2                                                      | -> | ON     |                                                                                                 |  |  |

|    | DIP1.3                                                      | -> | OFF    |                                                                                                 |  |  |

|    | DIP1.4                                                      | -> | ON     |                                                                                                 |  |  |

|    | DIP1.5                                                      | -> | OFF    |                                                                                                 |  |  |

|    | DIP1.6                                                      | -> | ON     |                                                                                                 |  |  |

|    | DIP1.7                                                      | -> | ON     |                                                                                                 |  |  |

|    | DIP1.8                                                      | -> | ON     |                                                                                                 |  |  |

| ITAL |                                                        |          | — grifo <sup>®</sup> ———                                                  | ®                                                                  |

|------|--------------------------------------------------------|----------|---------------------------------------------------------------------------|--------------------------------------------------------------------|

| 2)   | Address where mapping <b>PIO</b><br>Control card used: | 01:      | 40H in a 256 bytes addr<br>8 bits address bus;<br>provided with signal /M |                                                                    |

|      |                                                        | -><br>-> |                                                                           |                                                                    |

|      | <b>J</b> 4                                             | ->       | 1-2                                                                       |                                                                    |

|      |                                                        | ->       | OFF                                                                       |                                                                    |

|      |                                                        | -><br>-> | OFF<br>OFF                                                                |                                                                    |

|      |                                                        | ->       | OFF                                                                       |                                                                    |

|      |                                                        | ->       | ON                                                                        |                                                                    |

|      |                                                        | ->       | ON                                                                        |                                                                    |

|      | DIP2.7                                                 | ->       | OFF                                                                       |                                                                    |

|      | DIP2.8                                                 | ->       | ON                                                                        |                                                                    |

|      | DIP1                                                   | ->       | Indifferent                                                               |                                                                    |

| 3)   | Address where mapping <b>PIO</b><br>Control card used: | 01:      | 2F680H in a 256 Kbyte<br>20 bits address bus;<br>Not provided with signa  |                                                                    |

|      | J2                                                     |          | -> Not connected                                                          |                                                                    |

|      | J3                                                     |          | -> 5-6 and 7-8                                                            |                                                                    |

|      | J4                                                     |          | -> 2-3                                                                    |                                                                    |

|      | DIP2.1                                                 | ->       | ON                                                                        |                                                                    |

|      |                                                        | ->       | OFF                                                                       | A 19 is not compared through 12                                    |

|      |                                                        | -><br>-> |                                                                           | A18 is not connected through J3<br>A19 is not connected through J3 |

|      |                                                        | ->       | ON Declarse dataress                                                      |                                                                    |

|      |                                                        | ->       | ON                                                                        |                                                                    |

|      |                                                        | ->       | ON                                                                        |                                                                    |

|      | DIP2.8                                                 | ->       | OFF                                                                       |                                                                    |

|      | DIP1.1                                                 | ->       | ON                                                                        |                                                                    |

|      | DIP1.2                                                 | ->       | OFF                                                                       |                                                                    |

|      |                                                        | ->       | OFF                                                                       |                                                                    |

|      |                                                        | ->       | ON                                                                        |                                                                    |

|      |                                                        | ->       | OFF                                                                       |                                                                    |

|      |                                                        | ->       | OFF                                                                       |                                                                    |

|      |                                                        | ->       | OFF                                                                       |                                                                    |

|      | DIP1.8                                                 | ->       | OFF                                                                       |                                                                    |

To easily locate the above mentioned components, please refer to figures 2, 6 and 19 in the previous pages.

- ITALIAN TECHNOLOGY

6U7

-999-0

Indicating the board base address with **<baseaddr>**, that is the address set using DIP1 and DIP2, as indicated in the previous paragraph, **PIO 01** internal registers are addressable as explained in the following table.

— grifo<sup>®</sup> -

| DEVICE      | REG.   | ADDRESS                                    | R/W                                        | PURPOSE                                            |

|-------------|--------|--------------------------------------------|--------------------------------------------|----------------------------------------------------|

|             | PPI1A  | <baseaddr>+00H</baseaddr>                  | R/W                                        | Port A data register, PPI 82C55 section 1.         |

|             | PPI1B  | <baseaddr>+01H</baseaddr>                  | R/W                                        | Port B data register, PPI 82C55 section 1.         |

| PPI 82C55 1 | PPI1C  | <baseaddr>+02H</baseaddr>                  | R/W                                        | Port C data register, PPI 82C55 section 1.         |

|             | PPI1RC | <baseaddr>+03H</baseaddr>                  | R/W                                        | Command and control register, PPI 82C55 section 1. |

|             | PPI2A  | <baseaddr>+04H</baseaddr>                  | Port A data register, PPI 82C55 section 2. |                                                    |

|             | PPI2B  | Port B data register, PPI 82C55 section 2. |                                            |                                                    |

| PPI 82C55 2 | PPI2C  | <baseaddr>+06H</baseaddr>                  | R/W                                        | Port C data register, PPI 82C55 section 2.         |

|             | PPI2RC | <baseaddr>+07H</baseaddr>                  | R/W                                        | Command and control register, PPI 82C55 section 2. |

|             | PPI3A  | <baseaddr>+08H</baseaddr>                  | R/W                                        | Port A data register, PPI 82C55 section 3.         |

|             | PPI3B  | <baseaddr>+09H</baseaddr>                  | R/W                                        | Port B data register, PPI 82C55 section 3.         |

| PPI 82C55 3 | PPI3C  | <baseaddr>+0AH</baseaddr>                  | R/W                                        | Port C data register, PPI 82C55 section 3.         |

|             | PPI3RC | <baseaddr>+0BH</baseaddr>                  | R/W                                        | Command and control register, PPI 82C55 section 3. |

|             | PPI4A  | <baseaddr>+0CH</baseaddr>                  | R/W                                        | Port A data register, PPI 82C55 section 4.         |

|             | PPI4B  | <baseaddr>+0DH</baseaddr>                  | R/W                                        | Port B data register, PPI 82C55 section 4.         |

| PPI 82C55 4 | PPI4C  | <baseaddr>+0EH</baseaddr>                  | R/W                                        | Port C data register, PPI 82C55 section 4.         |

|             | PPI4RC | <baseaddr>+0FH</baseaddr>                  | R/W                                        | Command and control register, PPI 82C55 section 4. |

| WATCH       |        | <baseaddr>+00H</baseaddr>                  | D                                          |                                                    |

| DOG         | WD     | <br><baseaddr>+0FH</baseaddr>              | R                                          | Watch Dog circuitery retrigger register.           |

FIGURE 21: INTERNAL REGISTERS ADDRESSING TABLE

| ITALIAN TECHNOLOGY | grifo <sup>®</sup> ——— |  | 202 |  |

|--------------------|------------------------|--|-----|--|

|--------------------|------------------------|--|-----|--|

PERIPHERAL DEVICES SOFTWARE DESCRIPTION

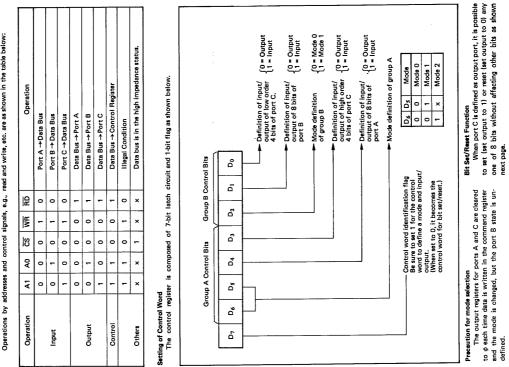

In the previous paragraphs are described the external registers addresses, while in this one there is a specific description of registers meaning and function (please refer to I/O addresses table, for the registers names and addresses values). For a more detailed description of the devices, please refer to manufacturing company documentation.

In the following paragraphs the  $D7 \div D0$  and  $.0 \div 7$  indications denote the eight bits of the combination used in I/O operations.

### WATCH DOG