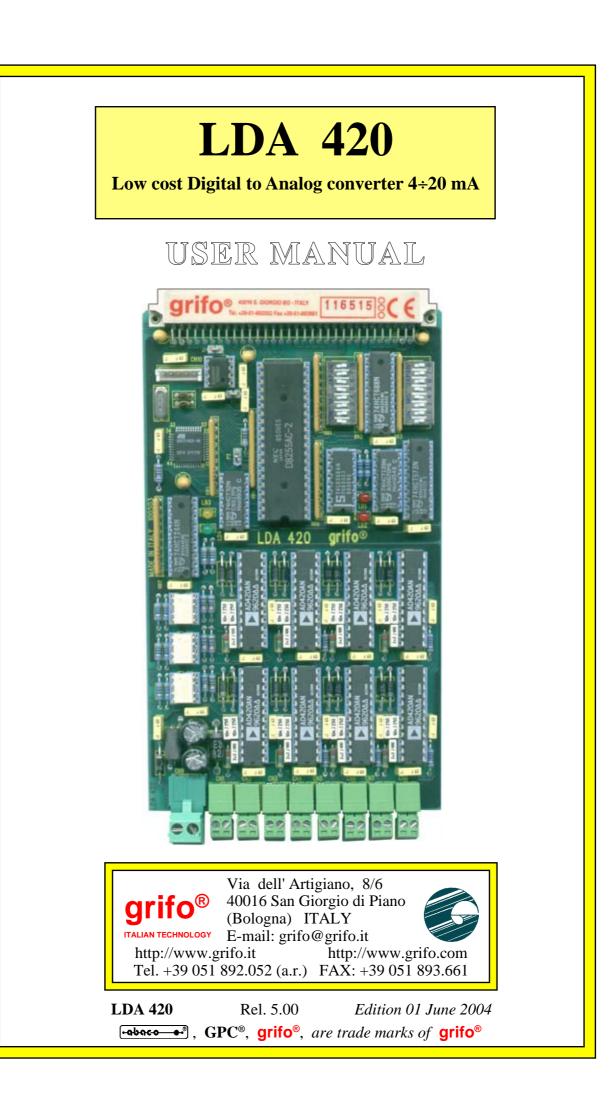

# LDA 420

Low cost Digital to Analog converter 4÷20 mA

## USER MANUAL

Single Euro format, with 100x160 mm dimension. 8 separated sections of D/A conversion, based on AD 420 component, 16 Bits resolution, with active 4÷20 mA output on furnished analog power supply voltage; 8 different protection and filter circuits. Wide range power supply input for analog section: 12÷32 V, 210 mA max. 8 screw terminal quick release, 2 pins connectors for generated analog signals; 1 screw terminal quick release, 2 pins connector for analog section power supply, not compatible with the analog output ones. Galvanic separation between analog section and control logic section. Four different configurations can be ordered, equipped wit 2,4,6,8 analog outputs. 8 ways dip switch for configuration and settings; visualization, through coloured LEDs, of the card status. Asynchronous **TTL serial** interface with configurable physic protocol; direct parallel interface to Abaco® Industrial BUS. On board CPU that manages the analog sections through commands received from serial or parallel interface; GNET logic communication protocol that allows the use of many units as slave devices connected on a serial line. Management firmware complete of **10** general purpose **commands** and with possibility to add interesting high level functions. 8 ways dip switch to set the allocation address of the card; used addressing space: 2 bytes; nornal addressing range of 256 bytes. Single power supply for control logic: +5 Vdc, 130 mA. Supplied with demo programs that simplify and speed the card use with each programmable external systems

No part of this document may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means, either electronic, mechanical, magnetic, optical, chemical, manual, or otherwise, without the prior written consent of **grifo**<sup>®</sup>.

## IMPORTANT

Although all the information contained herein have been carefully verified, **grifo**<sup>®</sup> assumes no responsability for errors that might appear in this document, or for damage to things or persons resulting from technical errors, omission and improper use of this manual and of the related software and hardware.

**grifo**<sup>®</sup> reserves the right to change the contents and form of this document, as well as the features and specification of its products at any time, without prior notice, to obtain always the best product.

For specific informations on the components mounted on the card, please refer to the Data Book of the builder or second sources.

## SYMBOLS DESCRIPTION

In the manual could appear the following symbols:

Attention: Generic danger

Attention: High voltage

Attention: ESD sensitive device

### **Trade Marks**

•abace••••, **GPC**<sup>®</sup>, **grifo**<sup>®</sup> : are trade marks of **grifo**<sup>®</sup>. Other Product and Company names listed, are trade marks of their respective companies.

\_<u>(-abaco</u>\_\_\_\_ -**--**®) (bu/)

# **GENERAL INDEX**

| INTRODUCTION                                            | 1  |

|---------------------------------------------------------|----|

| HARDWARE AND FIRMWARE VERSION                           | 2  |

| GENERAL INFORMATION                                     |    |

| CPU                                                     |    |

| MEMORY DEVICES                                          |    |

| SERIAL COMMUNICATION                                    |    |

| BUS INTERFACE                                           |    |

| STATUS AND CONFIGURATION                                |    |

| ANALOG SECTION                                          | 6  |

| TECHNICAL FEATURES                                      | 8  |

| GENERAL FEATURES                                        |    |

| PHYSICAL FEATURES                                       |    |

| ELECTRIC FEATURES                                       | 9  |

| INSTALLATION                                            | 10 |

| CONNECTIONS                                             | 10 |

| CN1+CN8 - D/A ANALOG OUTPUT CONNECTORS                  |    |

| CN9 - ANALOG POWER SUPPLY CONNECTOR                     |    |

| CN10 - SERIAL LINE CONNECTOR                            | 14 |

| K1 - CONNECTOR FOR ABACO <sup>®</sup> BUS               | 16 |

| I/O CONNECTIONS                                         |    |

| VISUAL SIGNALATIONS                                     |    |

| JUMPERS                                                 |    |

| 2 PINS JUMPERS                                          |    |

| RESET AND POWER ON                                      |    |

| INTERRUPT                                               |    |

| POWER SUPPLY                                            | 22 |

| ADDRESSES AND MAPS                                      | 24 |

| PERIPHERAL MAPPING                                      |    |

| COMMUNICATION REGISTERS ADDRESSING                      |    |

| PARALLEL COMMUNICATION MANAGEMENT                       | 25 |

| SOFTWARE DESCRIPTION                                    |    |

| GENERATED CURRENT AND CORRESPONDING COMBINATIONS        |    |

| LOGIC PROTOCOL                                          |    |

| ACQUISITION OF CURRENT COMBINATION OF AN ANALOG CHANNEL |    |

| SETTING OF CURRENT COMBINATION OF AN ANALOG CHANNEL     |    |

| SET ALL ANALOG OUTPUTS TO BEGINNING OF SCALE            |    |

| ACQUISITION OF CONFIGURATION DIP SWITCH STATUS          |    |

| SET ACTIVITY LEDS STATUS                                |    |

| OVERALL STATUS ACQUISITION                              | 31 |

| (•••••••••••••••••••••••••••••••••••• | grifo <sup>®</sup> ——— | ITALIAN TECHNOLOGY |

|---------------------------------------|------------------------|--------------------|

|---------------------------------------|------------------------|--------------------|

| ACQUISITION OF IDENTIFICATION NAME      | 31  |

|-----------------------------------------|-----|

| SETTING OF IDENTIFICATION NAME          | 32  |

| ACQUISITION OF ANALOG CHANNELS PRESENCE | 32  |

| ACQUISITION OF FIRMWARE VERSION         | 32  |

| COMMUNICATION EXAMPLE                   |     |

| EXTERNAL CARDS                          | 35  |

| BIBLIOGRAPHY                            | 38  |

| APPENDIX A: COMMANDS LIST               |     |

| APPENDIX B: ALPHABETICAL INDEX          | B-1 |

## **FIGURE INDEX**

| FIGURE 1: BLOCK DIAGRAM                                    | 5  |

|------------------------------------------------------------|----|

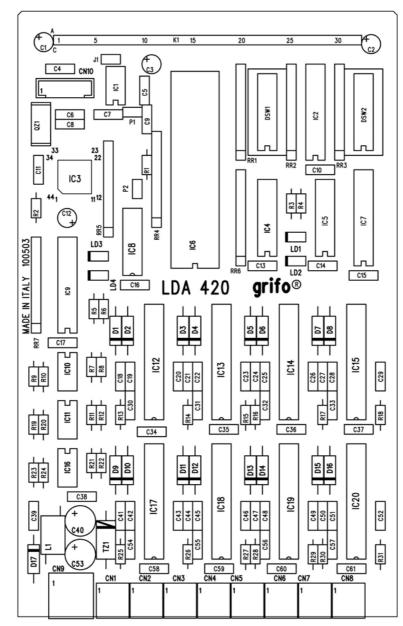

| FIGURE 2: COMPONENTS MAP (COMPONENTS SIDE)                 | 7  |

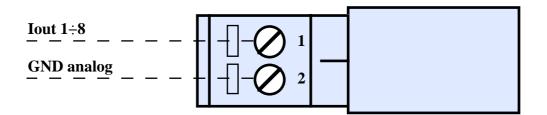

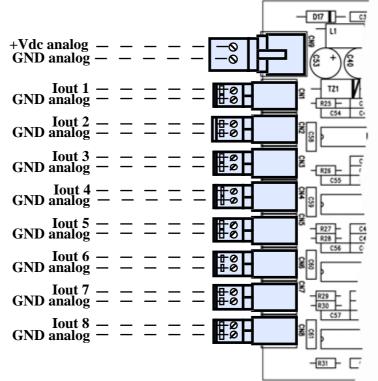

| FIGURE 3: CN1+CN8 - D/A ANALOG OUTPUT CONNECTORS           | 10 |

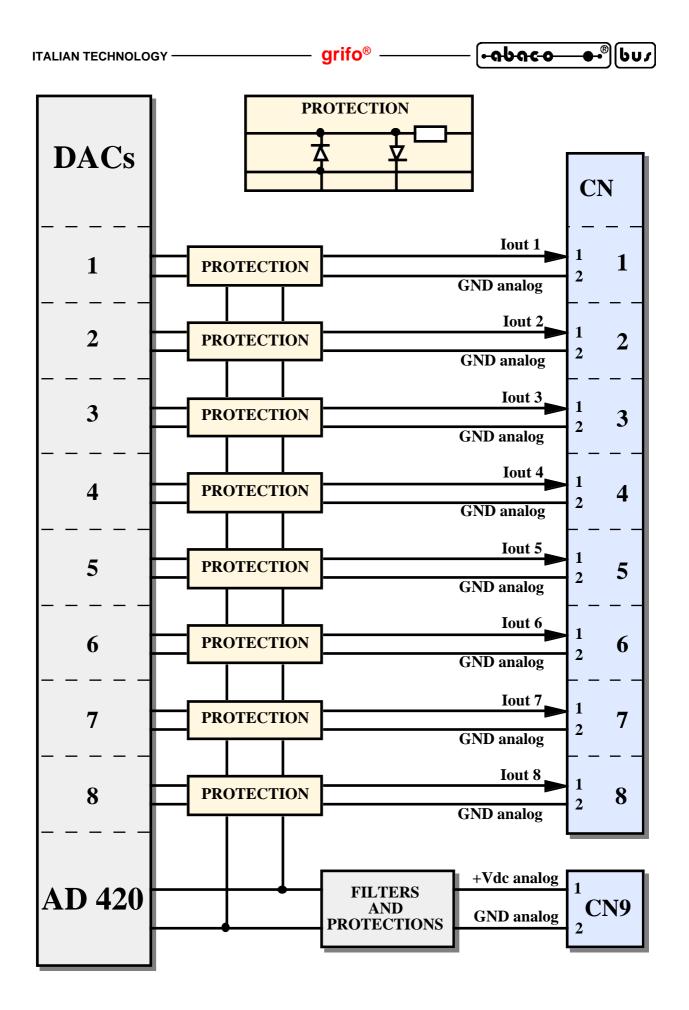

| FIGURE 4: D/A SECTION CONNECTIONS BLOCK DIAGRAM            | 11 |

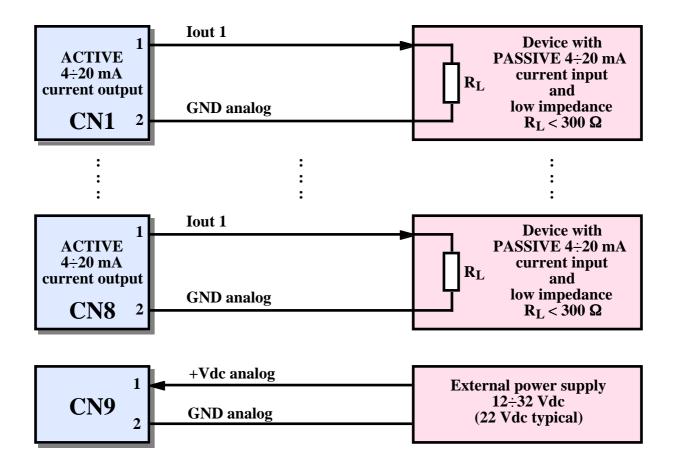

| FIGURE 5: CONNECTION OF ANALOG OUTPUTS TO EXTERNAL DEVICES | 12 |

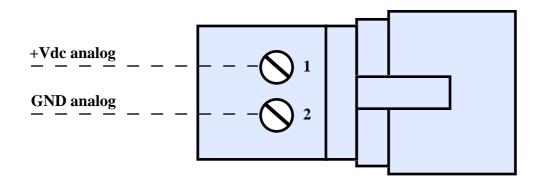

| FIGURE 6: CN9 - ANALOG POWER SUPPLY CONNECTOR              |    |

| FIGURE 7: ANALOG SIGNALS LOCATION                          |    |

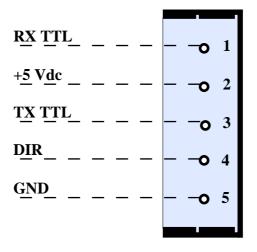

| FIGURE 8: CN10 - SERIAL LINE CONNECTOR                     |    |

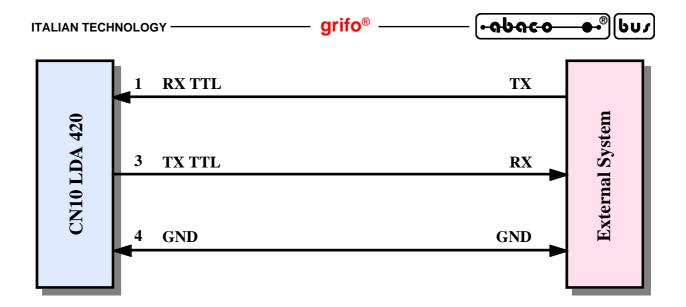

| FIGURE 9: TTL SERIAL CONNECTION EXAMPLE                    |    |

| FIGURE 10: CONNECTION THROUGH MSI 01 SERIAL INTERFACE      |    |

| FIGURE 11: K1 - CONNECTOR FOR ABACO <sup>®</sup> BUS       |    |

| FIGURE 12: LEDS TABLE                                      |    |

| FIGURE 13: LEDs, CONNECTORS, DIS SWITCH, ETC. LOCATION     |    |

| FIGURE 14: JUMPERS SUMMARIZING TABLE                       |    |

| FIGURE 15: 2 PINS JUMPERS TABLE                            |    |

| FIGURE 16: JUMPERS LOCATION                                |    |

| FIGURE 17: COMPONENTS MAP (SOLDER SIDE)                    |    |

| FIGURE 18: REGISTERS ADDRESSING TABLE                      |    |

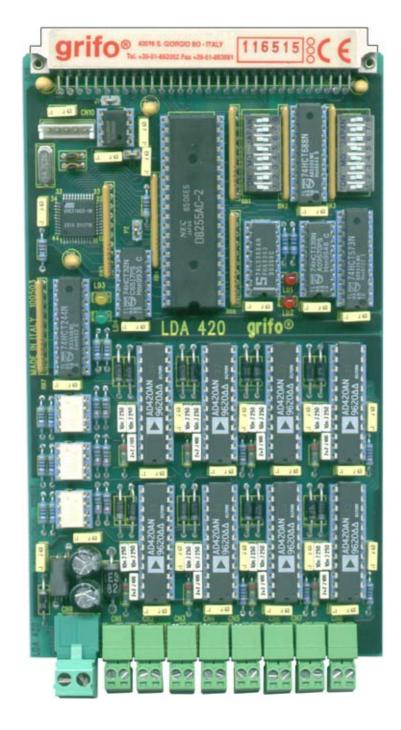

| FIGURE 19: PHOTO OF THE PERIPHERAL                         |    |

| FIGURE 20: POSSIBLE CONNECTIONS DIAGRAM                    |    |

| FIGURE A-1: COMMANDS SUMMARIZING TABLE                     |    |

|                                                            |    |

#### INTRODUCTION

The use of these devices has turned - IN EXCLUSIVE WAY - to specialized personnel. This device is not a **<u>safe component</u>** as defined in directive <u>**98-37/CE**</u>.

Pins of Mini Module are not provided with any kind of ESD protection. They are connected directly to their respective pins of microcontroller. Mini Module is affected by electrostatic discharges. Personnel who handles Mini Modules is invited to take all necessary precautions to avoid possible damages caused by electrostatic discharges.

The purpose of this handbook is to give the necessary information to the cognizant and sure use of the products. They are the result of a continual and systematic elaboration of data and technical tests saved and validated from the manufacturer, related to the inside modes of certainty and quality of the information.

The reported data are destined- IN EXCLUSIVE WAY- to specialized users, that can interact with the devices in safety conditions for the persons, for the machine and for the environment, impersonating an elementary diagnostic of breakdowns and of malfunction conditions by performing simple functional verify operations, in the height respect of the actual safety and health norms.

The informations for the installation, the assemblage, the dismantlement, the handling, the adjustment, the reparation and the contingent accessories, devices etc. installation are destined - and then executable - always and in exclusive way from specialized warned and educated personnel, or directly from the TECHNICAL AUTHORIZED ASSISTANCE, in the height respect of the manufacturer recommendations and the actual safety and health norms.

The devices can't be used outside a box. The user must always insert the cards in a container that rispect the actual safety normative. The protection of this container is not threshold to the only atmospheric agents, but specially to mechanic, electric, magnetic, etc. ones.

To be on good terms with the products, is necessary guarantee legibility and conservation of the manual, also for future references. In case of deterioration or more easily for technical updates, consult the AUTHORIZED TECHNICAL ASSISTANCE directly.

To prevent problems during card utilization, it is a good practice to read carefully all the informations of this manual. After this reading, the user can use the general index and the alphabetical index, respectly at the begining and at the end of the manual, to find information in a faster and more easy way.

HARDWARE AND FIRMWARE VERSION

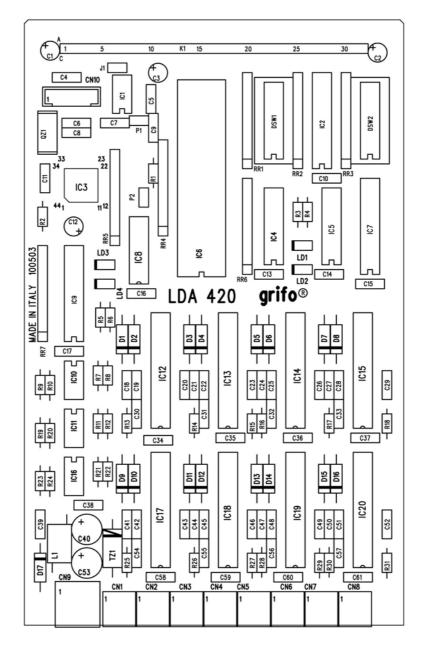

The present handbook is reported to the **LDA 420** card release **100503** and to firmware version **1.1**. The validity of the bring informations is subordinate to the number of the card release. The user must always verify the correct correspondence among the two denotations. On the card the release number is present in more points both board printed diagram (serigraph) and printed circuit (for example near resistor network RR7 on the component side) and the firmware version is reported on a label put on the CPU, which is component called IC3. Also, firmware version can be requested directly to the peripheral using a specific serial command.

#### GENERAL INFORMATION

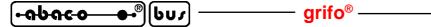

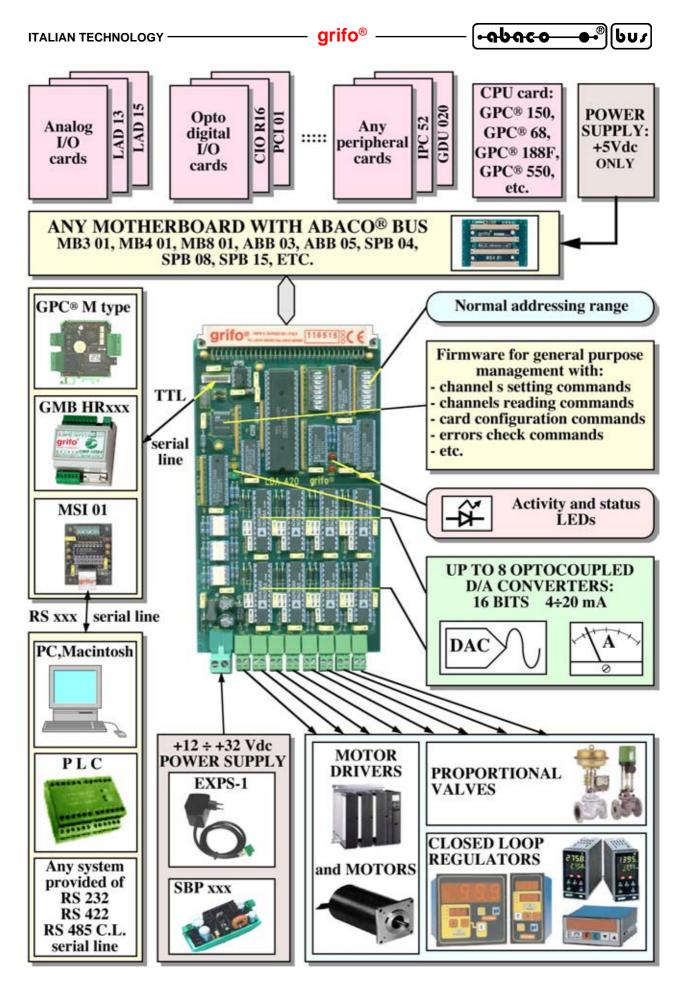

LDA 420 is an inexpensive and powerful peripheral device, in Eurocard format, featuring BUS ABACO<sup>®</sup> interface.

It belongs to the analog peripherals listing, in detail its purpose is to provide up to 8 Digital to Analog conversion signals, each one can output a current in the range  $4 \div 20$  mA, with 16 bits of resolution. Locally generated analog signals are available on a comfortable quick release screw terminal connector, located in the front side, for faster and easier cabling.

Generation of analog signals is made by eight indipendent D/A conversion circuits and as many filtering and protection circuits, to reduce interferences and nois on the signals.

**LDA 420** is modulare, that is it can be ordered with the desired number of outputs (up to 8), to allow a further optimization of costs, according to the application to build.

LDA 420 can be ordered in one of these configurations: LDA 420, LDA 420/4, LDA 420/6 and LDA 420/8 featuring respectively two, four, six and eight current outputs in the range 4÷20 mA.

Regardless of the configuration, **LDA 420** is always delivered with an input for analog section power supply, which is also connected to a screw terminal.

The choice to use an external voltage to supply analog section avoids problems of power dissipation and voltage level of current loop controlled on board, increasing the fields of use.

Other remarkable features of **LDA 420** are the galvanic separation between control logic and analog section, which makes **LDA 420** suitable also for electrically noisy industrial environments, and the presence of a local CPU, to have a software management easier and faster.

Functionalities of **LDA 420** are coded in its firmware, executed on the local CPU, and can be easily expanded on user request, making possible, for example, the generation of ramps, preset analog profiles, repeated and proportional settings, etc.

LDA 420 can be driven through the parallel BUS by any **grifo®** GPC® xxx intelligent module connectable to BUS ABACO®, where LDA 420 takes as low as two contiguous bytes, or it can be driven through serial port by any card provided with a programmable asynchronous line.

- Single Eurocard format, with 100x160 mm dimension

- 8 separated sections of D/A conversion, based on AD 420 component, 16 Bits resolution, with active 4÷20 mA output on furnished analog power supply voltage

- 8 different protection and filter circuits

- Wide range power supply input for analog section: 12÷32 V, 210 mA max

- 8 screw terminal quick release, 2 pins connectors for generated analog signals

## ITALIAN TECHNOLOGY \_\_\_\_\_\_ grifo<sup>®</sup> \_\_\_\_\_

- 1 screw terminal quick release, 2 pins connector for analog section power supply, not compatible with the analog output ones

- Galvanic separation between analog section and control logic section

- Four different configurations can be ordered, equipped wit 2,4,6,8 analog outputs

- 8 ways **dip switch** for configuration and settings

- Visualization, through coloured LEDs, of the card status

- Asynchronous TTL serial interface with configurable physic protocol

- Direct parallel interface to Abaco® Industrial BUS

- On board CPU that manages the analog sections through commands received from **serial** or **parallel** interface

- **GNET** logic communication protocol that allows the use of many units as slave devices connected on a serial line

- Management firmware complete of **10** general purpose **commands** and with possibility to add interesting high level functions

- 8 ways dip switch to set the allocation address of the card

- Used addressing space: 2 bytes; nornal addressing range of 256 bytes

- Single power supply for control logic: +5 Vdc, 130 mA

- Supplied with **demo programs** that simplify and speed the card use with each programmable external systems

- Possibility of special executions of custom programs, also for small quantities

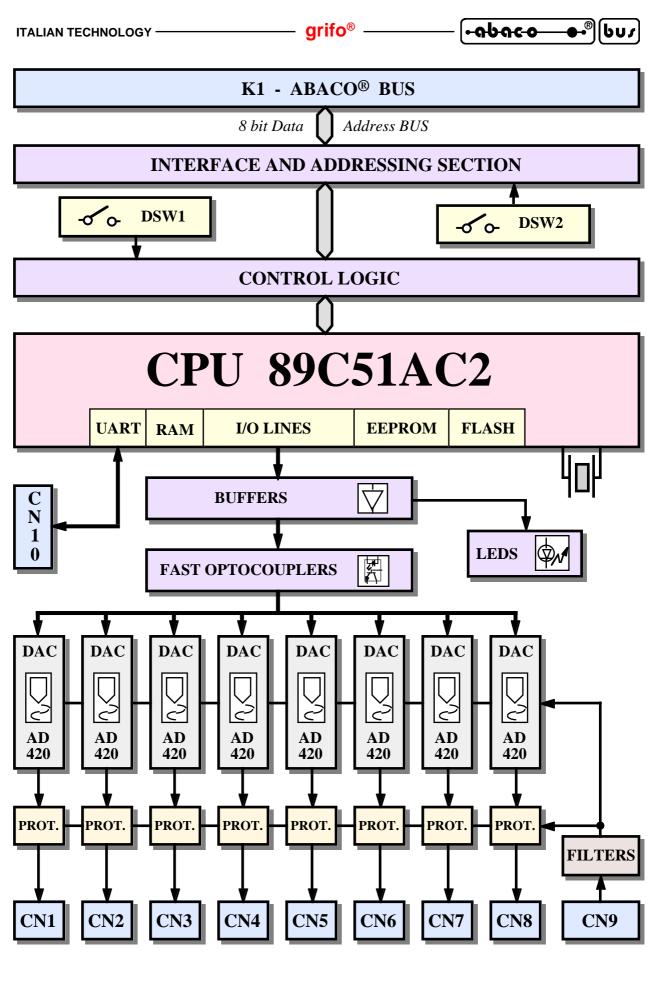

Here follows a description of the board's functional blocks, with an indication of the operations performed by each one. To easily recognize the blocks, please refer to figure 1.

#### <u>CPU</u>

LDA 420 uses processor Atmel AT89C51AC2.

This microprocessor manages completely the peripheral, allowing it to operate in autonomy and the master to perform operation control without wasting time for driving the output signals. In fact, CPU takes care of communication and of signals setting, configuration and control, starting from data ready to use and so easy to manipulate.

#### **MEMORY DEVICES**

LDA 420 features three memory devices, inside the CPU:

- FLASH EPROM for management firmware code;

- Work RAM for firmware and parameters;

- EEPROM for storing configurations;

Size of these memories are immutable and have been decided according to peripheral operativity. Their management is made completely by the firmware and the user is not involved at all.

#### SERIAL COMMUNICATION

Serial communication to the external world is made by an **asynchronous full duplex** TTL serial line that, using specific external converters (like **grifo**<sup>®</sup> **MSI 01**) can be buffered as RS 232, RS 485, RS 422 or passive current loop.

Please remark that serial lines RS 422, RS 485 and current loop and the powerful logic communication protocol included in the firmware allow to connect up to 128 **LDA 420** in a network, using only 2 or 4 wires.

This means to be able to have intelligent units located at high distances, capable to drive a great number of signals, remote controlled by only the serial communication cables.

For further information about the physical and logical communication protocol please contact **grifo**<sup>®</sup> directly.

#### **BUS INTERFACE**

It is possible to use a parallel interface, other than the above mentioned serial interface, to communicate faster with LDA 420, parallel interface of LDA 420 is called BUS ABACO<sup>®</sup>.

This section manages the data exchange between control logic and command device (**CPU** or **GPC**<sup>®</sup>), in detail it manages the peripheral BUS addressing trough a dip switch called DSW2.

BUS **ABACO**<sup>®</sup> addressing uses 8 bits and allows access to 256 different addresses. For further information please refer to chapter "ADDRESSES AND MAPS".

In addition, using a mother board like **grifo<sup>®</sup> ABB 03** or **grifo<sup>®</sup> ABB 05**, it is possible to use BLOCK format control devices for ABACO<sup>®</sup> I/O BUS.

This feature allows to expand the application with a good price/performance rate and so makes it suitable to solve several problems of industrial automation.

Please refer to chapter "EXTERNAL CARDS" for a brief description of control devices.

#### **STATUS AND CONFIGURATION**

An 8 pins dip switch has been installed to configure the peripheral and application functions.

Acquiring the status of these 8 signals, the user can manage several working conditions, without having to employ other signals to do that.

The firmware can use this dip switch to select some operating conditions, as described in furthere paragraphs.

All the status and configuration resources are completely managed by firmware through specific commands or can indicate faulty conditions in autonomy.

FIGURE 1: BLOCK DIAGRAM

LDA 420

*Rel.* 5.00

#### ANALOG SECTION

This section includes the analog signals management and generation circuitery and is based on eight indipendent 16 bits D/A converters (AD420), each one of them provides an output current signal in the range 4÷20 mA.

grifo<sup>®</sup>

These outputs are connected to eight protection and filtering circuits and become available to the user on a specific comfortable screw terminal connector.

Opportune buffers and fast optocouplers separate analog section and digital section to cancel any reciprocal interference; this warrants the correct working of the unit under any operative condition and remarkable stability and precision.

Analog output sections number can be configured, in default version only two signals are available and the remaining 6 are optional, that is they are installed only if they are requested in the commercial order.

In detail, LDA 420 can be delivered in one of the following configurations:

| default version | -> | 2 D/A that is 2 analog outputs in the range $4\div 20$ mA                 |

|-----------------|----|---------------------------------------------------------------------------|

| version /4      | -> | 4 D/A that is <b>4</b> analog outputs in the range $4 \div 20 \text{ mA}$ |

| version /6      | -> | 6 D/A that is <b>6</b> analog outputs in the range $4 \div 20 \text{ mA}$ |

| version /8      | -> | 8 D/A that is 8 analog outputs in the range 4÷20 mA                       |

Every output is <u>active</u>, that is it can generate the programmed output current starting from a specific <u>external supply</u> and so can be connected directly to passive devices.

For further information about signals type, connection and required power supply please refer to further paragraphs and chapters.

Programming of analog section components is made by local CPU, which can can drive every D/A installed through its I/O signals and the firmware.

A set of firmware commands allow the user to decide the status of generated signals according to the requirements of application to make.

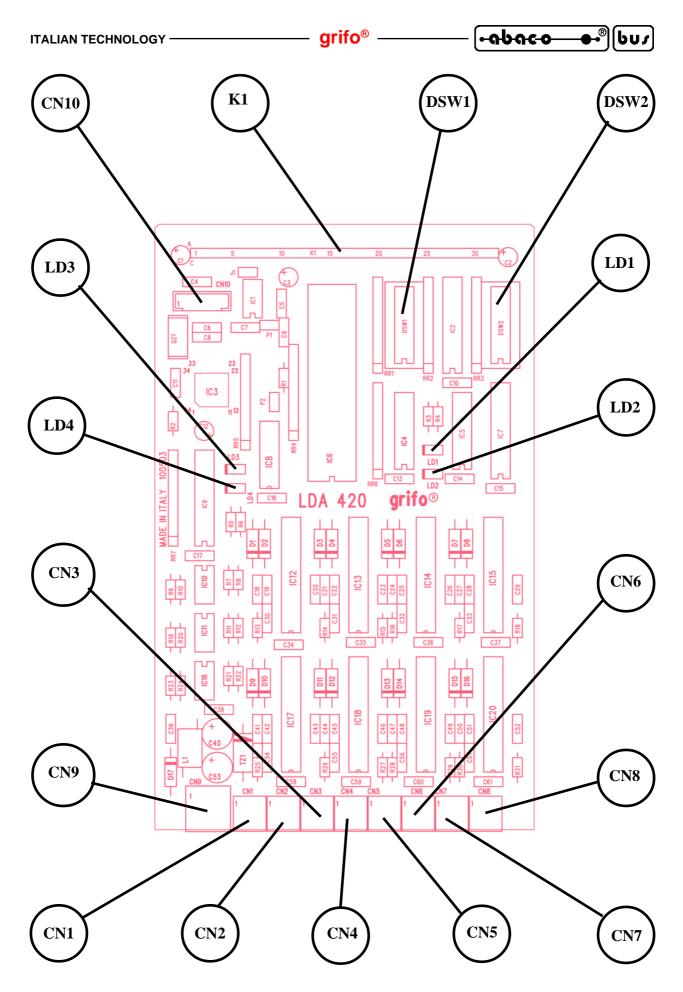

FIGURE 2: COMPONENTS MAP (COMPONENTS SIDE)

TECHNICAL FEATURES

#### **GENERAL FEATURES**

| BUS type:                  | ABACO®                                                                                                                                                                                                                                                                                                                                |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Addressable Range:         | 256                                                                                                                                                                                                                                                                                                                                   |

| Bytes taken:               | 2                                                                                                                                                                                                                                                                                                                                     |

| Local resources:           | <ul> <li>analog outputs in the range 4÷20 mA</li> <li>protection and filtering sections</li> <li>D/A converter with resolution 16 bits</li> <li>fast optocoupler section</li> <li>TTL asynchronous serial line</li> <li>configration 8 pins dip switch</li> <li>address setting 8 pins dip switch</li> <li>indication LEDs</li> </ul> |

| Local peripherals:         | 8 AD420                                                                                                                                                                                                                                                                                                                               |

| Local CPU:                 | ATMEL AT89c51AC2 with quartz 14.7456 MHz                                                                                                                                                                                                                                                                                              |

| Local memory:              | IC3: FLASH EPROM 32KBytes<br>RAM 1280 Bytes<br>EEPROM 2KBytes                                                                                                                                                                                                                                                                         |

| Physical serial protocol:  | please contact grifo <sup>®</sup>                                                                                                                                                                                                                                                                                                     |

| Analog output resolution:  | 16 bits                                                                                                                                                                                                                                                                                                                               |

| D/A channel settling time: | 3.8 msec                                                                                                                                                                                                                                                                                                                              |

| Reset time:                | 80 msec                                                                                                                                                                                                                                                                                                                               |

| Interrupt activation time: | 5 µsec                                                                                                                                                                                                                                                                                                                                |

| Firmware commands:         | 10                                                                                                                                                                                                                                                                                                                                    |

#### **PHYSICAL FEATURES**

| Size:       | Eurocard standard format 100 x 160 mm                  |

|-------------|--------------------------------------------------------|

| Weight:     | 170 g max                                              |

| Connectors: | K1: DIN 41612, 64 pins, male, 90 degreeses, A+C type C |

| Page 8      | LDA 420 Rel. 5.00                                      |

|                                  | grifo <sup>®</sup>                                                                                                                                                                                                                                                                                                                                                                                       | • จษจะ •                                                                                                                                                                                                   | - <b>●●</b> ® し <i>∪ょ</i>                                                                                                                                            |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                  | CN1: quick release screw termina<br>CN2: quick release screw termina<br>CN3: quick release screw termina<br>CN4: quick release screw termina<br>CN5: quick release screw termina<br>CN6: quick release screw termina<br>CN7: quick release screw termina<br>CN8: quick release screw termina<br>CN8: quick release screw termina<br>CN9: quick release screw termina<br>CN9: quick release screw termina | al, 2 pins, 90 deg,<br>al, 2 pins, 90 deg | <ul> <li>3.5 mm pitch</li> </ul> |

| Temperature range:               | From 0 to 70 °C                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                            |                                                                                                                                                                      |

| Relative humidity:               | 20% up to 90% (without conden                                                                                                                                                                                                                                                                                                                                                                            | se)                                                                                                                                                                                                        |                                                                                                                                                                      |

| ELECTRIC FEATURES                |                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                            |                                                                                                                                                                      |

| Power supply:                    | +5 Vdc ±5%.                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                            |                                                                                                                                                                      |

| Digital current consumption:     |                                                                                                                                                                                                                                                                                                                                                                                                          | Ilt configuration)<br>t consumption)                                                                                                                                                                       |                                                                                                                                                                      |

| Analog power supply voltage:     | 12 ÷ 32 Vdc (t                                                                                                                                                                                                                                                                                                                                                                                           | ypical 22 Vdc)                                                                                                                                                                                             |                                                                                                                                                                      |

| Analog current consumption:      |                                                                                                                                                                                                                                                                                                                                                                                                          | t configuration)<br>t consumption)                                                                                                                                                                         |                                                                                                                                                                      |

| Output current range of D/A:     | 4.0000 ÷ 20.00                                                                                                                                                                                                                                                                                                                                                                                           | 000 mA                                                                                                                                                                                                     |                                                                                                                                                                      |

| Offset:                          | ±0.0020 mA                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                            | (*)                                                                                                                                                                  |

| Linearity:                       | ±0.0030 mA                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                            | (*)                                                                                                                                                                  |

| Repetibility on the same channe  | <b>±</b> 0.0010 mA                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                            | (*)                                                                                                                                                                  |

| Max difference of output current | nt on all channels: ±0.0100 mA                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                            | (*)                                                                                                                                                                  |

| Total noise:                     | ±0.0001 mA                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                            | (*)                                                                                                                                                                  |

| Max error due to power supply    | ±0.0300 mA                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                            | (*)                                                                                                                                                                  |

| Max error due to temperature:    | ±0.0070 mA                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                            | (*)                                                                                                                                                                  |

| Maximum resistance connectab     | <b>de:</b> $300 \Omega$                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                            | (*)                                                                                                                                                                  |

(\*) Data reported here are referred to a typical +Vdcanalog (analog power supply) +22 Vdc

#### INSTALLATION

In this chapter there are the information for a right installation and correct use of **LDA 420**. In detail there are the locations and functions of each connector, of the user LEDs, jumpers, dip switches, etc.

- grifo® -

#### **CONNECTIONS**

LDA 420 has 11 connectors that can be linkeded to other devices or directly to the field, according to system requirements.

In this paragraph there are connectors pin out, a short signals description (including the signals direction) and connectors location (see figure 13 to easily locate them).

#### CN1÷CN8 - D/A ANALOG OUTPUT CONNECTORS

CN1÷CN8 are eight 2 pins quick release screw terminal connector, 90 degreeses, pitch 3.5 mm. These connectors feature the eight current analog outputs 4÷20 mA generated by **LDA 420**, ready to be connected to the external world.

Connectors are located in the frontal to easy the connection and signals location is designed to reduce the interferences as much as possible.

FIGURE 3: CN1+CN8 - D/A ANALOG OUTPUT CONNECTORS

Signals description:

| Iout n  | = | O - D/A n-th current output signal, in the range $4 \div 20$ mA. |

|---------|---|------------------------------------------------------------------|

| D/A GND | = | - Ground of analog output signals.                               |

Connectors CN1÷CN8 are always present while some of the corresponding analog signals are available only if **LDA 420** is opportunely configured.

Following figures show the connection modalities for all analog outputs both locally and externally; in specific figure 7 allows to locate more easily the positions both of signals and of connectors.

FIGURE 4: D/A SECTION CONNECTIONS BLOCK DIAGRAM

As can be seen on figure 4, every analog output is provided with its own protection circuitery which prevents damages and breakings in case of connection to incompatible devices.

Such circuitery keeps the voltage in the current loop between the limits of analog power supply (+Vdcanalog) through the two clamping diodes and keeps the amount of current circulating in the allowed range (serie resistor).

Anamog power supply (+Vdcanalog) is required to supply the whole section and to proved the current for the outputs installed. These latter are therfore ACTIVE outputs so they must be connected to PASSIVE devices capable to accept a supplied current loop.

Following figure shows the connection modality of external devices with indications about their analog input stage: such stage should be ideal (impedance = 0), but in real applications impedance must be lower than 300  $\Omega$ .

For further information about analog outputs please refer to paragraph "ELECTRIC FEATURES".

FIGURE 5: CONNECTION OF ANALOG OUTPUTS TO EXTERNAL DEVICES

#### grifo<sup>®</sup> -

#### **CN9 - ANALOG POWER SUPPLY CONNECTOR**

CN9 is a 2 pins quick release screw terminal connector, 90 degreeses, pitch 5.12 mm. Power supply for analog section must be connected to CN9, it is required to make the **LDA 420** work correctly.

CN9 is on the frontal side to easy connection.

Signals description:

| +Vdc analog | = I - Analog power supply signal: $12 \div 32$ Vdc (typical is 22 Vdc). |

|-------------|-------------------------------------------------------------------------|

| GND analog  | = - Ground of analog output signals.                                    |

For further information about analog power supply please refer to paragraph "POWER SUPPLY". The figure below shows signals location on the connectes dedicated to analog outputs seen from the component side of **LDA 420**.

FIGURE 7: ANALOG SIGNALS LOCATION

LDA 420 Rel. 5.00

#### **CN10 - SERIAL LINE CONNECTOR**

CN10 is a 5 pins low profile, vertical, male connector pitch 2.54 mm.

CN10 features all the signals for TTL serial communication, that is digital power supply, TX and RX signals plus a third signal (direction) in case of network communication.

Pins location is designed to reduce interferences as much as possible and to easy the connection. Female connector for CN10 can be ordered to **grifo**<sup>®</sup> by specifing code CC.RS422 in the order, which corresponds to a set of 5 colored wires one meter long, crimped on a 5 pins female connector.

FIGURE 8: CN10 - SERIAL LINE CONNECTOR

Signals description:

| RX TTL | = I - Receive Data: TTL serial reception signal.          |

|--------|-----------------------------------------------------------|

| TX TTL | = O - Transmit Data: TTL serial transmission signal.      |

| DIR    | = O - Direction or handshake signal for TTL serial line.  |

| +5 Vdc | = O - Positive terminal of $+5$ Vdc digital power supply. |

| GND    | = - Ground of analog output signals.                      |

|        |                                                           |

For further information about serial line configuration and its communication modalities, please contact **grifo**<sup>®</sup> directly, while for further information about how to connect this device both to other TTL devices and to devices with another serial line protocol, please refer to the following figures.

FIGURE 9: TTL SERIAL CONNECTION EXAMPLE

Surely the conversion interface **MSI 01** is the most comfortable solution to convert a TTL serial line of **LDA 420** into a RS 232, RS 422, RS 485 or current loop serial line.

As already indicated in chapter "SERIAL COMMUNICATION" these electric protocols allow to connect **LDA 420** event at remarkable distances, through electrically noisy environments and even making networks at low cost.

|              | 1 RX TTL | RXD 5  |

|--------------|----------|--------|

| 420          | 3 TX TTL | TXD 2  |

| CN10 LDA 420 | 5 DIR    | /RTS 3 |

| 410 L        | 2 +5 Vdc | Vcc 1  |

| Ċ            | 4 GND    | GND 6  |

|              |          |        |

FIGURE 10: CONNECTION THROUGH MSI 01 SERIAL INTERFACE

## ໌<del>-ດຽດແລ\_\_\_\_®</del>][ບບ*s*] \_\_\_\_\_\_ grifo® -

- ITALIAN TECHNOLOGY

#### **K1 - CONNECTOR FOR ABACO® BUS**

The connector for **ABACO<sup>®</sup> industrial BUS**, called K1 on the board, is a DIN 41612, male, a 90 °, type C, A+C.

Here follows the pin-out of the connector installed on LDA 420, in addition there is the standard 8 bits and 16 bitsABACO<sup>®</sup> BUS pin-out.

Please remark that all the signals here described are TTL, except for the power supplies.

| Row A      | Row A     | K1 A    | DIN | K1 C    | Row C     | Row C      |

|------------|-----------|---------|-----|---------|-----------|------------|

| 16 bit BUS | 8 bit BUS | LDA 420 | PIN | LDA 420 | 8 bit BUS | 16 bit BUS |

| GND        | GND       | GND     | 1   | GND     | GND       | GND        |

| +5 Vdc     | +5 Vdc    | +5 Vdc  | 2   | +5 Vdc  | +5 Vdc    | +5 Vdc     |

| D0         | D0        | D0      | 3   | N.C.    | -         | D8         |

| D1         | D1        | D1      | 4   | N.C.    | -         | D9         |

| D2         | D2        | D2      | 5   | N.C.    | -         | D10        |

| D3         | D3        | D3      | 6   | /INT    | /INT      | /INT       |

| D4         | D4        | D4      | 7   | N.C.    | /NMI      | /NMI       |

| D5         | D5        | D5      | 8   | N.C.    | /HALT     | D11        |

| D6         | D6        | D6      | 9   | N.C.    | /MREQ     | /MREQ      |

| D7         | D7        | D7      | 10  | /IORQ   | /IORQ     | /IORQ      |

| A0         | A0        | A0      | 11  | /RD     | /RD       | /RDLDS     |

| A1         | A1        | A1      | 12  | /WR     | /WR       | /WRLDS     |

| A2         | A2        | A2      | 13  | N.C.    | /BUSAK    | D12        |

| A3         | A3        | A3      | 14  | N.C.    | /WAIT     | /WAIT      |

| A4         | A4        | A4      | 15  | N.C.    | /BUSRQ    | D13        |

| A5         | A5        | A5      | 16  | N.C.    | /RESET    | /RESET     |

| A6         | A6        | A6      | 17  | /M1     | /M1       | /IACK      |

| A7         | A7        | A7      | 18  | N.C.    | /RFSH     | D14        |

| A8         | A8        | N.C.    | 19  | N.C.    | /MEMDIS   | /MEMDIS    |

| A9         | A9        | N.C.    | 20  | N.C.    | VDUSEL    | A22        |

| A10        | A10       | N.C.    | 21  | N.C.    | /IEI      | D15        |

| A11        | A11       | N.C.    | 22  | N.C.    | -         | -          |

| A12        | A12       | N.C.    | 23  | N.C.    | CLK       | CLK        |

| A13        | A13       | N.C.    | 24  | N.C.    | -         | /RDUDS     |

| A14        | A14       | N.C.    | 25  | N.C.    | -         | /WRUDS     |

| A15        | A15       | N.C.    | 26  | N.C.    | -         | A21        |

| A16        | -         | N.C.    | 27  | N.C.    | -         | A20        |

| A17        | -         | N.C.    | 28  | N.C.    | -         | A19        |

| A18        | -         | N.C.    | 29  | N.C.    | /R.T.     | /R.T.      |

| +12 Vdc    | +12 Vdc   | N.C.    | 30  | N.C.    | -12 Vdc   | -12 Vdc    |

| +5 Vdc     | +5 Vdc    | +5 Vdc  | 31  | +5 Vdc  | +5 Vdc    | +5 Vdc     |

| GND        | GND       | GND     | 32  | GND     | GND       | GND        |

FIGURE 11: K1 - CONNECTOR FOR ABACO® BUS

LDA 420 Rel. 5.00

\_\_\_\_\_ grifo<sup>®</sup> -

Signals description:

8 bits CPU

| A0-A15      | = | 0   | - Address BUS             |

|-------------|---|-----|---------------------------|

| D0-D7       | = | I/O | - Data BUS                |

| INT         | = | Ι   | - Interrupt request       |

| NMI         | = | Ι   | - Non Maskable Interrupt  |

| HALT        | = | 0   | - Halt state              |

| MREQ        | = | 0   | - Memory Request          |

| IORQ        | = | 0   | - Input Output Request    |

| RD          | = | 0   | - Read cycle status       |

| WR          | = | 0   | - Write cycle status      |

| BUSAK       | = | 0   | - BUS Acknowledge         |

| WAIT        | = | Ι   | - Wait                    |

| BUSRQ       | = | Ι   | - BUS Request             |

| RESET       | = | 0   | - Reset                   |

| M1          | = | 0   | - Machine cycle one       |

| RFSH        | = | 0   | - Refresh for dynamic RAM |

| MEMDIS      | = | Ι   | - Memory Display          |

| VDUSEL      | = | 0   | - VDU Selection           |

| IEI         | = | Ι   | - Interrupt Enable Input  |

| CLK         | = | 0   | - System clock            |

| <b>R.B.</b> | = | Ι   | - Reset button            |

| +5 Vdc      | = | Ι   | - Power supply at +5 Vdc  |

| +12 Vdc     | = | Ι   | - Power supply at +12 Vdc |

| -12 Vdc     | = | Ι   | - Power supply at -12 Vdc |

| GND         | = |     | - Ground signal           |

|             |   |     |                           |

16 bits CPU

| A16-A22       | _ | 0   | - Address BUS             |

|---------------|---|-----|---------------------------|

| 1110-1122     | _ | 0   |                           |

| D8-D15        | = | I/O | - Data BUS                |

| <b>RD UDS</b> | = | 0   | - Read Upper Data Strobe  |

| WR UDS        | = | 0   | - Write Upper Data Strobe |

| IACK          | = | 0   | - Interrupt Acknowledge   |

| RD LDS        | = | 0   | - Read Lower Data Strobe  |

| WR LDS        | = | 0   | - Write Lower Data Strobe |

#### NOTE

Directionality indications as above stated are referred to a master (**GPC**<sup>®</sup>) board and have been kept untouched to avoid ambiguity in case of multi-boards systems.

#### **I/O CONNECTIONS**

To prevent possible connecting problems between **LDA 420** and the external systems, the user has to read carefully the previous paragraph information and must follow these instrunctions:

grifo<sup>®</sup>

- For RS 232, RS 422, RS 485, current loop and TTL signals the user must follow the standard rules of each one of these protocols;

- For all TTL signals the user must follow the rules of this electric standard. The connected digital signal must be always referred to card digital ground and if an electric insulation is necessary, then an opto coupled interface must be connected. For TTL signals, the 0V level corresponds to logic state 0, while 5V level corrisponds to logic state 1.

- The analog outputs must be connected to low impedance passive inputs: using a shielded cable reduces the electric noise. Eventual connections to power actuators (motors), must be made through a specific power driver circuits, e.g., activation or inverter.

- To take advantage of **LDA 420** galvanic separation, it must be supplied using two separated tensions from two different sources, that must be galvanically separated too.

- Analog power supply must be proviede by a source that generates no electric noise, perfectly stable and indipendent from any external factor like temperature, radio frequincies, etc.

#### VISUAL SIGNALATIONS

**LDA 420** features 4 LEDs described in the following table:

| LED | COLOUR | PURPOSE                                                                                                                           |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------|

| LD1 | Red    | Visualizes parallel communication interrupt activation (interrupt request from LDA 420 to CPU master on BUS ABACO <sup>®</sup> ). |

| LD2 | Red    | When parallel communication is used, it turns ON when a data is received.                                                         |

| LD3 | Yellow | Activity LED manageable through a specific command and general malfunction indication.                                            |

| LD4 | Green  | Activity LED manageable through a specific command.                                                                               |

#### FIGURE 12: LEDS TABLE

The main function of LEDs is to inform the user about status, with a simple visual indication and in addition to this, LEDs make easier the debug and test operations of the complete system.

Firmware turns LEDs ON and OFF automatically, according to the situation and the conditions and provides further visual indications about status and malfunctioning.

To recognize the LED location on the card, please refer to figure 13.

FIGURE 13: LEDS, CONNECTORS, DIP SWITCH, ETC. LOCATION

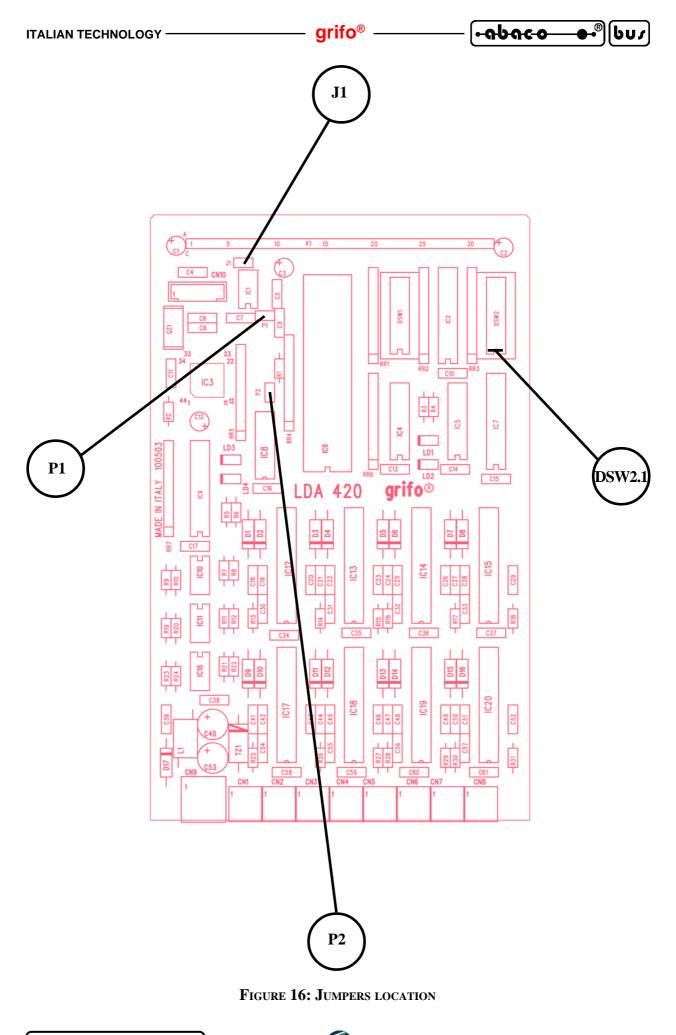

#### JUMPERS

On **LDA 420** there are 3 jumpers and two dip switches for working mode configuration. Here below is the jumpers list, location and function:

| JUMPER | PER N° PINS PURPOSE |                                                                                          |

|--------|---------------------|------------------------------------------------------------------------------------------|

| J1     | 2                   | Connects parallel communication request signals to interrupt on BUS ABACO <sup>®</sup> . |

| P1     | 2                   | Reset contacts (please see paragraph POWER ON AND RESET).                                |

| P2     | 2                   | Selects CPU operating mode.                                                              |

| DSW2.1 | 2                   | Enables management of signal /M1 coming from BUS ABACO <sup>®</sup> .                    |

#### FIGURE 14: JUMPERS SUMMARIZING TABLE

The following tables describe all the right connections of LDA 420 jumpers with their relative functions.

To recognize these valid connections, please refer to the board printed diagram (serigraph) or to figure 2 of this manual, where the pins numeration is listed; for recognizing jumpers location, please refer to figure 16.

The "\*" denotes the default connection, or on the other hand the connection set up at the end of testing phase, that is the configuration the user receives.

#### 2 PINS JUMPERS

| JUMPER       | CONNECTION                                                                        | PURPOSE                                                                                                | DEF. |

|--------------|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|------|

| J1           | not connected                                                                     | Does not connect parallel communication request signal to interrupt on BUS <b>ABACO</b> <sup>®</sup> . | *    |

| connected    |                                                                                   | Connects parallel communication request signal to interrupt on BUS ABACO <sup>®</sup> .                |      |

| D1           | not connected                                                                     | On board CPU reset signal, not actived.                                                                |      |

| P1 connected |                                                                                   | On board CPU reset signal kept actived.                                                                |      |

|              | not connected                                                                     | Selects RUN mode for on board CPU.                                                                     | *    |

| P2 connected |                                                                                   | Selects DEBUG mode for on board CPU. (reserved to <b>grifo</b> <sup>®</sup> technicians).              |      |

| DSW2.1       | not connected Circuitery to interface BUS ABACO <sup>®</sup> d manage signal /M1. |                                                                                                        | *    |

| D5 W 2.1     | connected                                                                         | Circuitery to interface BUS ABACO <sup>®</sup> manages signal /M1.                                     |      |

#### FIGURE 15: 2 PINS JUMPERS TABLE

LDA 420 Rel. 5.00

#### **RESET AND POWER ON**

**LDA 420** is provided with a reset circuitery that manages the always critical phase of turining on and at the same time it monitors continuously digital power supply voltage, to avoid problems due to misuse.

After activation and consequent deactivation of reset circuitery, **LDA 420** restart the execution of management firmware in a condition where all outputs are set to the beginning og the scale (4 mA). This circuitery decides also the time elapsed between its activation and firmware restart: 50 msec in case of reset and 80 msec in case of power on.

Possible reset sources are jumper P1 and power supply control circuitery but remarkable is the fact that <u>/RESET signal of BUS **ABACO**<sup>®</sup> (pin 16 of connector K1) is not connected, so **LDA 420** in NOT aware of reset CPU or GPC<sup>®</sup> reset signals.</u>

Pins of P1 can be connected to a normally open contact (e.g. a push button) and when the contact is closed (the pins are short-circuited) reset circuitery activates with opportune timings.

Its main purpose is to exit from infinite loop conditions, especially during debug phase, and to execute the application program from the beginning without having to disconnect power supply/ To easily locate reset contact, please refer to figure 16.

#### **INTERRUPT**

LDA 420 generates an interrupt request when the local CPU must send a data to the control system on BUS ABACO<sup>®</sup> or when it is in condition to reveice a data from this latter.

By hardware, it is possible to connect this request to /INT signal on BUS **ABACO**<sup>®</sup> (pin 6C of connector K1), and LED LD1 shows its status.

Main purpose of interrupt signal is to ask the attention of the control system when it is possible a bidirectional data exchange, it is easy to see that this signal allows to optimize management times, in fact control system must not poll for the status of **LDA 420**.

Interrupt signal remains in active status for 5 µsec, to allow a correct management also in case of contemporary interrupts generated by other peripherals.

#### **POWER SUPPLY**

LDA 420 requires two power supplies:

- for digital section supply must be +5 Vdc ± 5%, that must be provided through the specific pins of connector K1. Tracks lay out has been designed to fetch digital supply from K1 and distribute it to all the point that require it; this explains the directionality reported in the signal descriptions and the connectors, where +5 Vdc is an input only on K1. For special cases the user can provide +5 Vdc also from different entry points, but <u>must</u> make a preventive correct working verification. A filtering circuitery efficent and distributed protects the local sections against disturbs or noise from the external world, to improve the overall working efficence.

| ITALIAN TECHNOLOGY | grifo <sup>®</sup> | (•ลษละอ          | ®_[b | US |

|--------------------|--------------------|------------------|------|----|

| ITALIAN TECHNOLOGY | grito <sup>©</sup> | (• <u>avac o</u> |      | U  |

<u>for analog section</u> supply must be in the range +12 ÷ +32 Vdc, that must be provided through the pins 1 and 9 of connector CN9 respecting the polarity. This voltage is used to supply the whole analog section including the current outputs, this means that its current consumption changes according to the configuration ordered. Typical voltage for this supply is +22 Vdc, that minimizes offset and linearity errors; EXPS-1 power supply generates this voltage starting from main power supply. Anolog voltage connected to CN9 passes through a filtering and protection circuitery, which includes also a TransZorb<sup>™</sup>, to prevent damages due to wrong voltages and breaking of supply section and to get a greater stability on the signals generated.

To warrant highest immunity against disturbs and so a correct working of the whole system, it is required that these two voltages are galvanically separated.

In other words the user must assure that signals GND and GNDanalog are electrically NOT connecrd.

For further information please refer to paragraph "ELECTRIC FEATURES".

FIGURE 17: COMPONENTS MAP (SOLDER SIDE)

ADDRESSES AND MAPS

This chapter provides all the hardware informations needed to use LDA 420 board.

Here the user will find informations about I/O space mapping and local peripheral devices addressing.

Of course, if **LDA 420** is configured for serial communication, all the information reported in this chapter are superfluous.

#### PERIPHERAL MAPPING

LDA 420 is mapped into a 2 contiguous bytes I/O addressing space, that can be mapped starting from different base addresses according to how the board is configured. This feature allows to use several LDA 420 on the same BUS ABACO<sup>®</sup>, or to install them on a BUS where other peripheral modules are installed obtaining a structure that can be expanded without any difficulty or modifications to the application software.

The base address can be defined through the specific BUS interface circuitry on the board itself; this circuitry uses the eight pins dip switch called **DSW2**, from which it reads the address set by the user. Here follows the corrispondance between dips configuration and address signals.

| DSW2.1 | -> | Not used (See paragraph "JUMPERS") |

|--------|----|------------------------------------|

| DSW2.2 | -> | Address A1                         |

| DSW2.3 | -> | Address A2                         |

| DSW2.4 | -> | Address A3                         |

| DSW2.5 | -> | Address A4                         |

| DSW2.6 | -> | Address A5                         |

| DSW2.7 | -> | Address A6                         |

| DSW2.8 | -> | Address A7                         |

|        |    |                                    |

These dips are driven in complemented logic, this means that if a switch is **ON** generates a **logic zero**, viceversa if a switch is **OFF** generates a **logic one**.

Dips DSW2.2 ÷ DSW2.8 allow to select the mapping address, ranging from 00H to FEH, covering a normal addressing range of 256 bytes where only even addresses (00H, 02H, ..., 0FEH) can be used. Also DSW2.1, described in the previous chapters, influences addressing logic and must be set according to which control system (**GPC**<sup>®</sup>) is used.

In detail, if this latter is provided with /M1 signal on BUS **ABACO**<sup>®</sup> connector, then DSW2.1 must be ON and viceversa.

Do not allocate more than one peripheral in the same addressing space (calculate also number of bytes taken), otherwise the BUS conflicts that may derive could prevent the overall system from working properly.

As an example, here follows a mapping description:

| ITALIAN TECHNOLOGY | – grifo <sup>®</sup> –––––– | (•ลษละอ | ⊢® | (bu <i>s</i> | <i>י</i> ] |

|--------------------|-----------------------------|---------|----|--------------|------------|

|--------------------|-----------------------------|---------|----|--------------|------------|

**LDA 420** should be mapped at address 192 = 0C0H, the control system is provided with signal /M1, mapping is done as follows:

| DSW2.1 | -> | ON  |

|--------|----|-----|

| DSW2.2 | -> | ON  |

| DSW2.3 | -> | ON  |

| DSW2.4 | -> | ON  |

| DSW2.5 | -> | ON  |

| DSW2.6 | -> | ON  |

| DSW2.7 | -> | OFF |

| DSW2.8 | -> | OFF |

|        |    |     |

To easily locate the components mentioned here, please refer to figures 13 and 16.

#### **COMMUNICATION REGISTERS ADDRESSING**

Indicating the board base address with **<baseaddr>**, that is the address set using dip switch DSW2, as indicated in the previous paragraph **LDA 420** internal registers are addressable as explained in the following table:

| REGISTER | ADDRESS                  | R/W | PURPOSE                                     |

|----------|--------------------------|-----|---------------------------------------------|

| STATUS   | <baseaddr>+00</baseaddr> | R   | Status register for parallel communication. |

| DATA     | <baseaddr>+01</baseaddr> | R/W | Data register for parallel communication.   |

#### FIGURE 18: REGISTERS ADDRESSING TABLE

As described in next paragraph, one register is read only while the other register irs readable and writeable, the first one indicates communication status, the second one is used for data exchange.

#### PARALLEL COMMUNICATION MANAGEMENT

This paragraph explains the software management modalities of the parallel communication between LDA 420 board and a master control unit.

The read/write DATA register, described in the previous table, allows to receive from and to transmit informations to the board, while the read only STATUS registers must be interpreted as follows:

*bit7 bit6 bit5 bit4 bit3 bit2 bit1 bit0* STATUS = **OBF IBF** NU NU NU NU NU NU

*Rel.* 5.00

LDA 420

| <b>⊷ຨຩຨຬ຺຺຺຺຺຺຺</b> | — grifo <sup>®</sup> —— | ITALIAN TECHNOLOGY |

|---------------------|-------------------------|--------------------|

|---------------------|-------------------------|--------------------|

where:

- NU = Not Used

- **IBF** = If active (1) indicates that the **LDA 420** board is ready to receive a new data; the master control unit can write it to the DATA register.

- **OBF** = If active (1) indicates that the **LDA 420** board has written a data into its transmission buffer; the master control unit can read the data performing a read operation of the DATA register.

After a Reset or a Power-On the master control unit must verify that the LDA 420 board has completed its initialization phase and is ready to receive data.

This condition is indicated by the logic state of the flags IBF and OBF, which must show the values: **IBF=1** and **OBF=0**.

The program running on the control board must start by performing a cycle (eventually timed out for more safety) to test the status of these signals and wait for the **LDA 420** board to be ready for the communication.

To show the above described modalities, here follow two examples subroutines written in CBZ 80:

```

"sendtolda"

REM Send to LDA 420 data contained in variable var%

REM Begin

DO

: REM Wait for bit IBF

st%=INP(stato%)

UNTIL ((st% AND &040)=&040)

: REM Send data to LDA 420

OUT dati%, var%

REM End

RETURN

"recfromIda"

REM Checks whether LDA 420 has sent a character; in such case character is returned

REM in variable var%, otherwise value -1 is returned

REM Begin

: REM Check status of bit OBF

st%=INP(stato%)

LONG IF ((st% AND &080)=&080)

var%=INP(dati%)

: REM Get data from LDA 420

XELSE

: REM LDA 420 sent no data

var%=-1

ENDIF

REM End

RETURN

```

#### grifo<sup>®</sup>

#### SOFTWARE DESCRIPTION

LDA 420 operativity is completely managed by its firmware which allows data exchange through serial line or BUS ABACO<sup>®</sup> parallel interface.

The firmware can recognize several commands and take actions in consequence: in practice it allows to set a value on the current outputs and to set/report information about peripheral configuration.

Next paragraph reports the description of the possible working modalities: description is mnemonic, ASCII and numeric, both in decimal and in hexadecimal.

Following description is referred to version 1.1; please remark that in case of specific needs, custom firmwares can be developed, so to create the best application.

For this latter evenience, please contact **grifo**<sup>®</sup> directly.

#### **GENERATED CURRENT AND CORRESPONDING COMBINATIONS**

Commands managed by firmware of **LDA 420**, in specific referred to analog outputs, are based on a 16 bit combination, which is the resolution of D/A converters and of the channels. Such combination has the following correspondence with generated Ioutn:

| 00000 = 0000H | -> | 4.0000 mA  |

|---------------|----|------------|

| 65535 = FFFFH | -> | 20.0000 mA |

this is a direct proportionality based on the current formula where the indipendent variable is the current desired in mA:

combination = Round(((Iout - 4) / 16) \* 65535)

and where *Round* function approximates to the closest integer number. From the above, it is possible to obtain the corresponding inverse formula that returns the currnent in mA from the combination:

Iout = ((combination / 65535) \* 16) + 4

Here follw some examples of combinations and corresponding generated currents:

| Iout in mA | -> | combination   |

|------------|----|---------------|

| 4.0000     | -> | 00000 = 0000H |

| 5.0000     | -> | 04096 = 1000H |

| 5.1000     | -> | 04506 = 119AH |

| 5.1100     | -> | 04546 = 11C2H |

| 5.1110     | -> | 04551 = 11C7H |

| 5.1113     | -> | 04552 = 11C8H |

| 12.0000    | -> | 32768 = 8000H |

| 20.0000    | -> | 65535 = FFFFH |

|            |    |               |

### LOGIC PROTOCOL

Logic protocol is the set of rules to code and organize data exchange to and from LDA 420, that is the rules that control system must follow to use properly the commands of LDA 420.

Logic protocol used by firmware is **GNET**: a **grifo**<sup>®</sup> legacy protocol designed and developed to peroform data exchange with any control unit and using both serial communication and parallel communication through BUS **ABACO**<sup>®</sup>.

For serial communication, as already indicated in this manual, please contact directly grifo<sup>®</sup>.

This protocol makes **LDA 420** <u>echo each received byte, so to avoid communication errors it is</u> <u>opportune to wait for the echo of the byte just sent before sending another one</u>.

The echo to wait for is the byte just sent.

Logic protocol for sending a command to LDA 420 is:

- 1) Send individual IDENTIFICATION NAME (128 ÷ 255).

- 2) Reception of echo.

- 3) Command code transmission ( $16 \div 127$ ).

- 4) Reception of echo.

- 5) Send most significant nibble  $(0 \div 15)$  of first parameter required by the command.

- 6) Reception of echo.

- 7) Send least significant nibble  $(0 \div 15)$  of first parameter required by the command.

- 8) Reception of echo.

:

- : :

- : : :

- N-3) Send most significant nibble  $(0 \div 15)$  of first parameter required by the command.

- N-2) Reception of echo.

- N-1) Send least significant nibble  $(0 \div 15)$  of first parameter required by the command.

- N) Reception of echo.

The only bytes that the control system must always send are the first and the second (numbers 1 and 3) to specify which **LDA 420** in the network has to execute the command and which command must be executed; all other bytes are optional as some commands may even require no parameters at all. Logic protocol used by **LDA 420** for communication of the eventual answer, after receiving a command, is:

#### N. BYTES RECEIVED FROM EXTERNAL SYSTEM

| INAL 51 |                                                                                    |         |         |          |        |          |        |          |        |        |      |      |

|---------|------------------------------------------------------------------------------------|---------|---------|----------|--------|----------|--------|----------|--------|--------|------|------|

| 1       | Most significant nibble $(0 \div 15)$ of first parameter returned by the command.  |         |         |          |        |          |        |          |        |        |      |      |

| 2       | Least significant nibble $(0 \div 15)$ of first parameter returned by the command. |         |         |          |        |          |        |          |        |        |      |      |

| :       |                                                                                    | :       | :       | :        | :      | :        | :      | :        | :      | :      | :    |      |

|         |                                                                                    |         |         |          |        |          |        |          |        |        |      |      |

| :       |                                                                                    | :       | :       | :        | :      | :        | :      | :        | :      | :      | :    |      |

| N-1     | Most sig                                                                           | nifican | ıt nibb | le (0 ÷  | 15) o  | f last p | arame  | eter ret | turned | by the | comm | and. |

| Ν       | Least sig                                                                          | nificar | nt nibb | ole (0 ÷ | -15) o | f last p | oarame | eter re  | turned | by the | comm | and. |

MEANING

This transmission begins only after LDA 420 has sent the echo of the last character received.

|  | — grifo <sup>®</sup> ——— |  | •®][bus] |

|--|--------------------------|--|----------|

|--|--------------------------|--|----------|

Interpretation, execution and eventual answer transmission of a command are performed only if IDENTIFICATION NAME sent to the network and the same value stored in non-volatile memory of excactly one **LDA 420** in the same network are equal.

So, before sending a command to a **LDA 420** the user must set its name with the specific commands. At first, the commands can be used referring to a name equal to 255, which makes the **LDA 420** always execute a command, regardless the name stored in memory.

Of course, this operation must be executed only once, when the **LDA 420** is installed, or in case of modifications of the application.

IDENTIFICATION NAME that the GNET protocol uses is the main element that allows to connect more than one **LDA 420** in a netword and is stored in a EEPROM memory, which does not lose its content even when power supply is turned off.

To clarify, we remark that in the following paragraphs with PARAMETER we mean the transmission or reception of two bytes corresponding to the two nibbles that make if (first bytes is most significant nibble, second byte is least significant nibble).