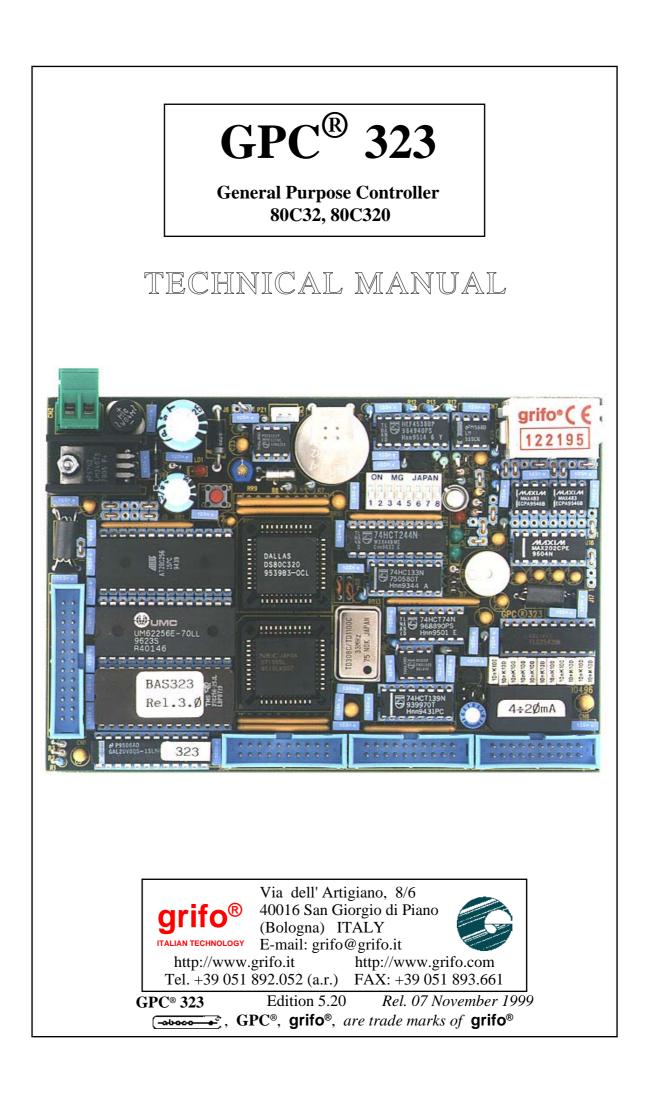

$GPC^{\mathbb{R}}$  323

General Purpose Controller 80C32, 80C320

# TECHNICAL MANUAL

Intelligent Abaco<sup>®</sup> BLOCK module, 100x50 mm size; Optional plastic mount for connection to **DIN 46277-1** and **DIN 46277-3**  $\hat{\Omega}$  rails; 14÷29 MHz 80C32 or 80C320 CPU; 96 KBytes maximum addressable memory; Sockets for 32K EPROM, 32K RAM, 32K EEPROM, RAM or EPROM; Back up circuitery for 32 KBytes RAM and optional RTC with 256 Bytes RAM through internal and external lithium battery; Optional serial EEPROM 512 to 2048 Bytes size; Eleven channels 12 Bits A/D Converter, +2,5V or 0÷20 mA full range, 10 µs conversion time; 24 TTL I/O signals;One Dip Switch with 5 pins software readable; Three 16 bits Timer-Counter with Capture and Compare registers; Watchdog; Two RS 232 serial lines, one of which settable in RS 422-485 or Current Loop; 26 pins Abaco<sup>®</sup> I/O BUS expansion connector; Two 20 pins I/O Abaco<sup>®</sup> standard connectors; One 20 pins Abaco® standard A/D connector; IDLE MODE or POWER DOWN MODE; Optional on-board power supply or external +5Vdc power supply; On board protection aganist voltage peaks by **TransZorb**<sup>TM</sup>; 4 status LEDs; 1 active buzzer.

## DOCUMENTATION COPYRIGHT BY grifo<sup>®</sup>, ALL RIGHTS RESERVED

No part of this document may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means, either electronic, mechanical, magnetic, optical, chemical, manual, or otherwise, without the prior written consent of **grifo**<sup>®</sup>.

### **IMPORTANT**

Although all the information contained herein have been carefully verified, **grifo**<sup>®</sup> assumes no responsability for errors that might appear in this document, or for damage to things or persons resulting from technical errors, omission and improper use of this manual and of the related software and hardware.

**grifo**<sup>®</sup> reserves the right to change the contents and form of this document, as well as the features and specification of its products at any time, without prior notice, to obtain always the best product.

For specific informations on the components mounted on the card, please refer to the Data Book of the builder or second sources.

# SYMBOLS DESCRIPTION

In the manual could appear the following symbols:

Attention: Generic danger

Attention: High voltage

### **Trade Marks**

GPC<sup>®</sup>, grifo<sup>®</sup> : are trade marks of grifo<sup>®</sup>. Other Product and Company names listed, are trade marks of their respective companies.

# **GENERAL INDEX**

| INTRODUCTION                               | 1  |

|--------------------------------------------|----|

| CARD VERSION                               | 1  |

| GENERAL FEATURES                           |    |

| CPU                                        | 3  |

| CLOCK                                      |    |

| POWER SUPPLY                               |    |

| SERIAL COMMUNICATION                       | 4  |

| MEMORY DEVICES                             |    |

| ON BOARD PERIPHERAL DEVICES                | 8  |

| ABACO® I/O BUS                             | 9  |

| CONTROL LOGIC                              | 9  |

| RESET KEY                                  | 9  |

| TECHNICAL FEATURES                         | 10 |

| GENERAL FEATURES                           | 10 |

| PHYSICAL FEATURES                          | 10 |

| ELECTRIC FEATURES                          | 11 |

| INSTALLATION                               | 12 |

| CONNECTIONS                                |    |

| CN 4 - POWER SUPPLY CONNECTOR              | 12 |

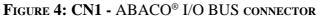

| CN1 - ABACO <sup>®</sup> I/O BUS CONNECTOR | 13 |

| CN7 - PPI 82C55 PORT A AND C I/O CONNECTOR |    |

| CN8 - PPI 82C55 PORT B I/O CONNECTOR       | 16 |

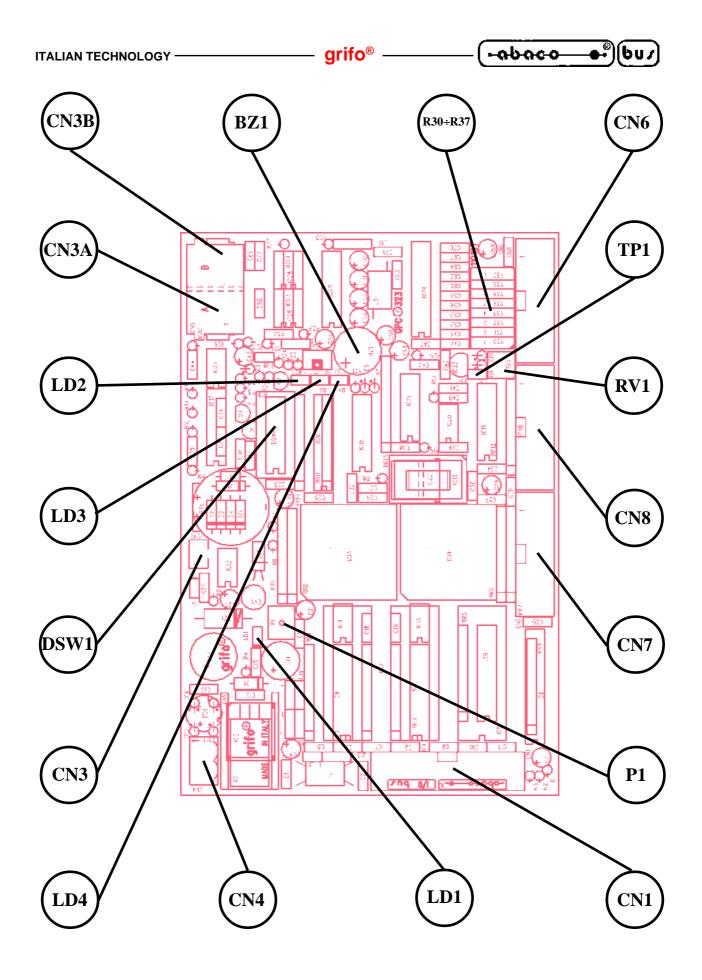

| CN6 - A/D CONVERTER INPUT CONNECTOR        | 18 |

| CN3A - SERIAL LINE A CONNECTOR             | 20 |

| CN3B - SERIAL LINE B CONNECTOR             | 26 |

| CN2 - EXTERNAL BACK UP BATTERY CONNECTOR   | 27 |

| OPERATOR INTERFACES                        | 27 |

| VISUAL FEEDBACK                            | 28 |

| I/O CONNECTION                             | 28 |

| RESET KEY                                  | 28 |

| TEST POINT                                 | 29 |

| DIP SWITCH                                 |    |

| POWER SUPPLY VOLTAGES                      |    |

| INTERRUPTS MANAGEMENT                      | 30 |

| TYPE OF ANALOG INPUT SELECTION             | 30 |

| TRIMMERS AND CALIBRATION                   | 31 |

| JUMPERS                                    | 32 |

| 2 PINS JUMPERS                             | 34 |

| 3 PINS JUMPERS                             | 36 |

| 6 PINS JUMPERS                             | 37 |

|                     | grifo <sup>®</sup> | ITALIAN TECHNOLOGY |

|---------------------|--------------------|--------------------|

| NOTE                |                    |                    |

| BACK UP             |                    |                    |

| SERIAL COMMUNICATIO | N TYPE SELECTION   |                    |

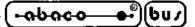

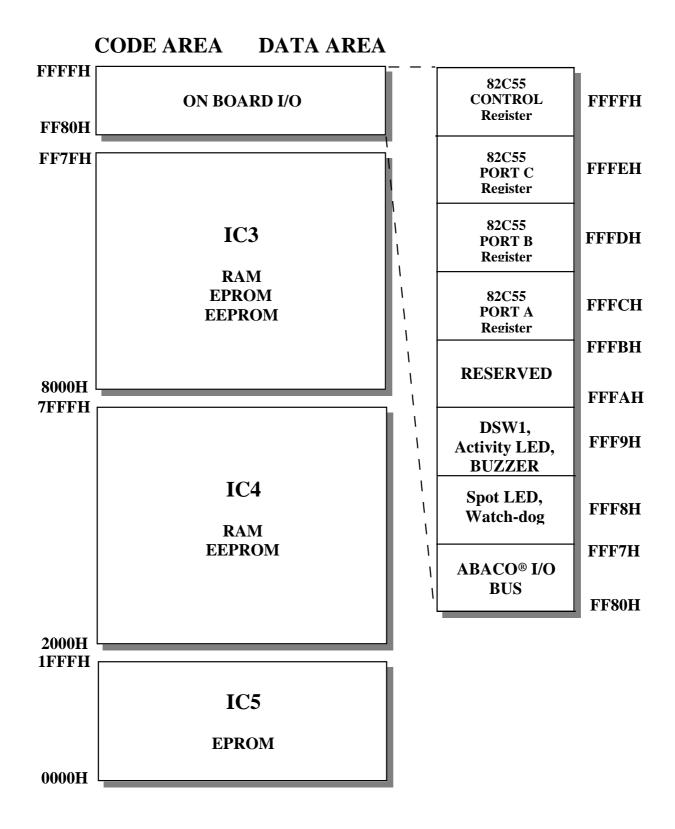

| MEMORY SELECTION       | 39 |

|------------------------|----|

| SOFTWARE               | 40 |

| HARDWARE               | 41 |

| INTRODUCTION           | 41 |

| ADDRESSES              | 41 |

| I/O ADDRESSES          | 42 |

| MEMORY ADDRESSES       | 42 |

| MEMORY CONFIGURATION 1 | 43 |

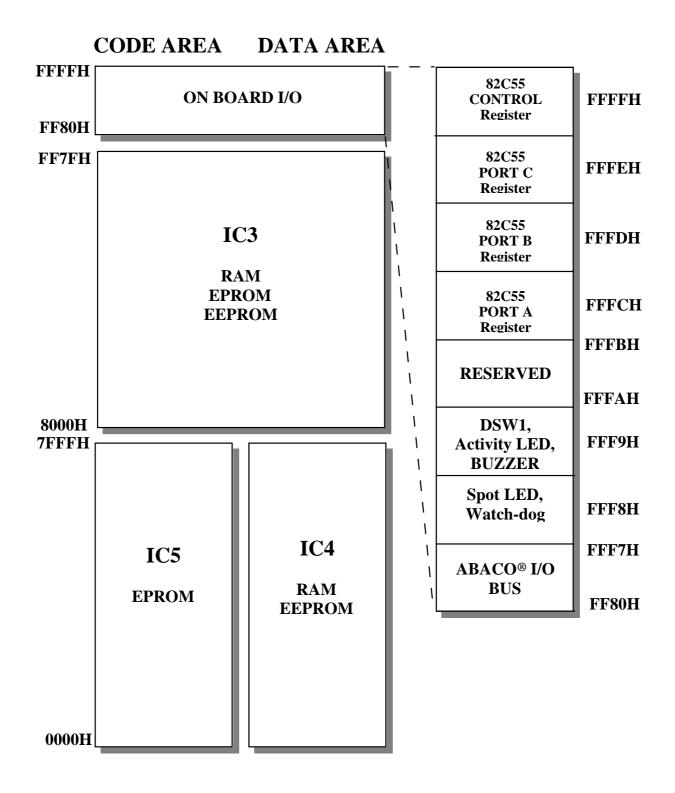

| MEMORY CONFIGURATION 3 | 44 |

| MEMORY CONFIGURATION 4 | 45 |

| PERIPHERAL DEVICES SOFTWARE DESCRIPTION     |     |

|---------------------------------------------|-----|

| DIP SWITCH                                  |     |

| ACTIVITY LED                                |     |

| EXTERNAL WATCHDOG                           |     |

| BUZZER                                      |     |

| SPOT LED                                    |     |

| PPI 82C55                                   |     |

| RS 422-485 COMMUNICATION DIRECTION          |     |

| SERIAL EEPROM                               |     |

| BACKED RAM + SERIAL RTC                     |     |

| A/D CONVERTER                               |     |

| SERIAL LINES                                |     |

| TIMER COUNTER                               |     |

| INTERNAL WATCH DOG                          |     |

| EXTERNAL DEVICES FOR GPC® 323               | 50  |

| BIBLIOGRAPHY                                |     |

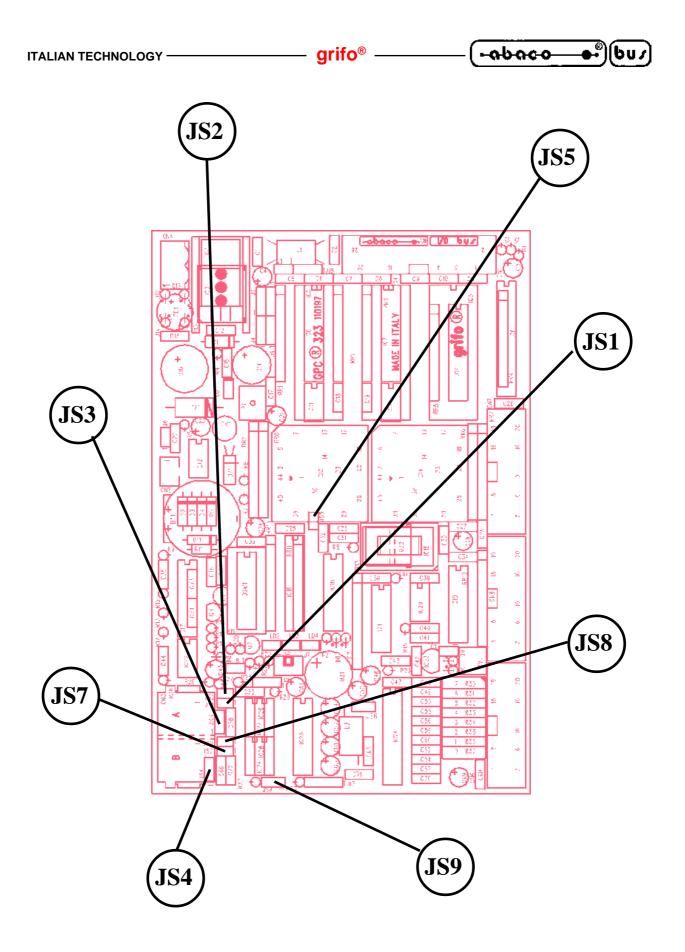

| APPENDIX A: JUMPERS LOCATION                | A-1 |

| APPENDIX B: ON BOARD PERIPHERAL DESCRIPTION | B-1 |

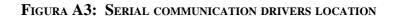

| μ <b>P 80C32</b>                            | B-1 |

| μ <b>Ρ 80C320</b>                           |     |

| APPENDIX C: ALPHABETICAL INDEX              | B-1 |

# FIGURE INDEX

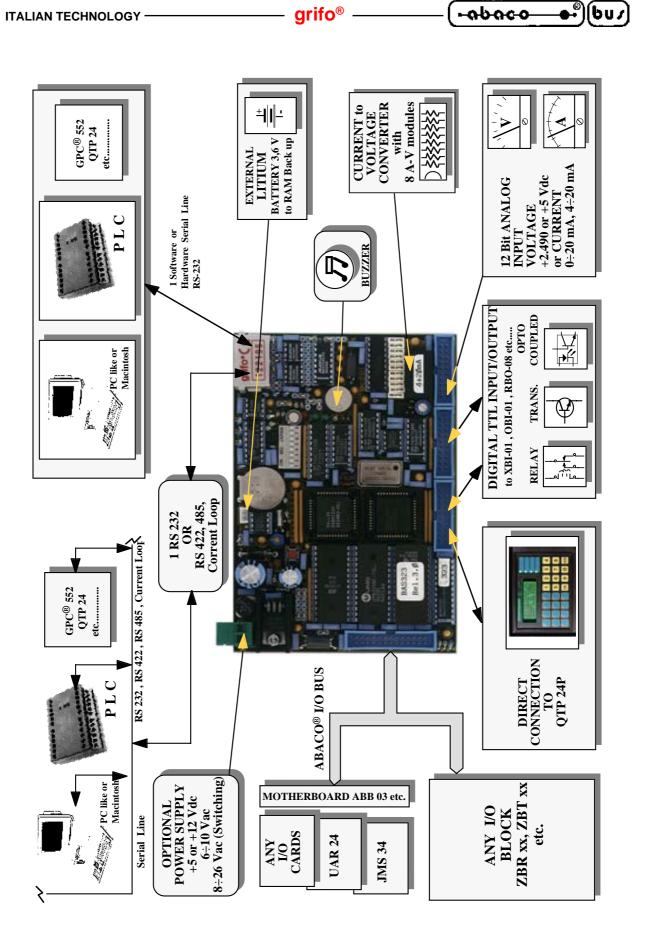

| Figure 1: Block diagram                                        | . 5 |

|----------------------------------------------------------------|-----|

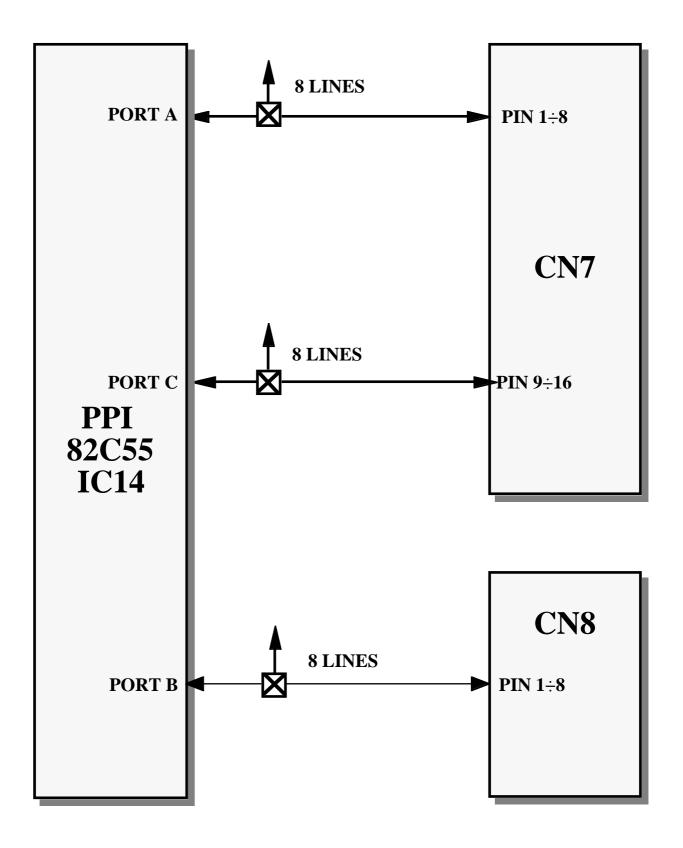

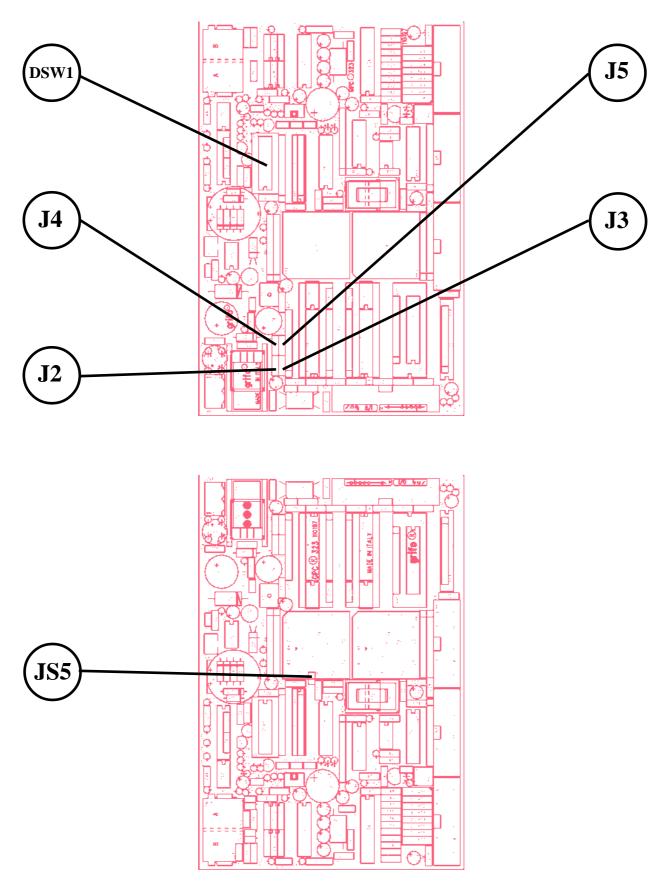

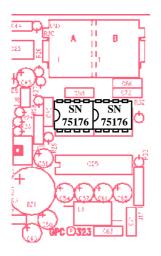

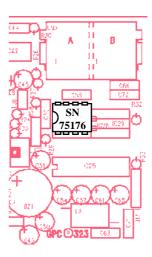

| FIGURE 2: COMPONENTS MAP                                       | . 7 |

| FIGURE 3: CN4 - POWER SUPPLY CONNECTOR                         | 12  |

| Figure 4: CN1 - ABACO <sup>®</sup> I/O BUS connector           |     |

| FIGURE 5: CN7 - PPI 82C55 PORT A AND C I/O CONNECTOR           | 14  |

| FIGURE 6: I/O SIGNALS CONNECTION DIAGRAM                       | 15  |

| FIGURE 7: CN8 - PPI 82C55 PORT B I/O CONNECTOR                 | 16  |

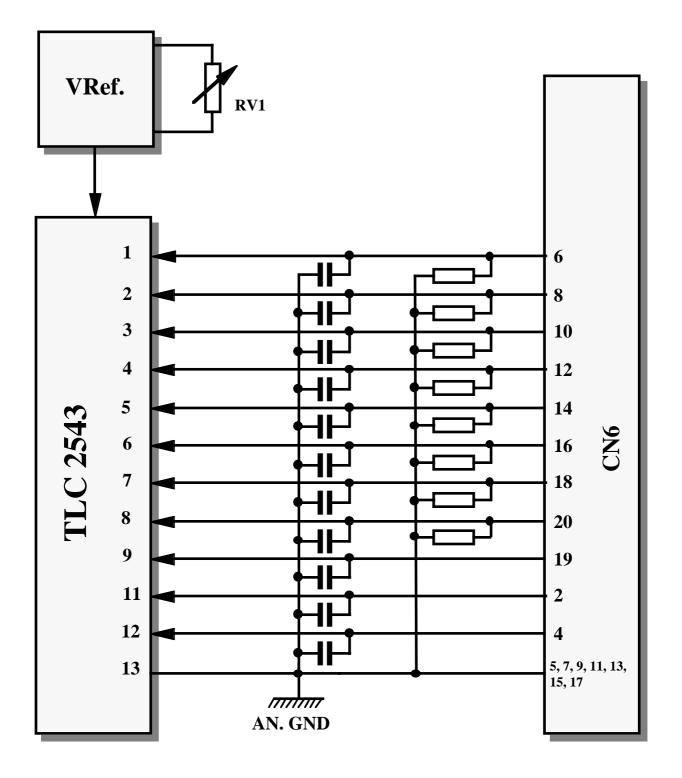

| FIGURE 8: LEDs, CONNECTORS, DIP SWITCH, ETC. LOCATION          | 17  |

| FIGURE 9: CN6 - A/D CONVERTER INPUT CONNECTOR                  | 18  |

| FIGURE 10: A/D CONVERTER INPUT BLOCK DIAGRAM                   | 19  |

| Figure 11: CN3A - Serial line A connector                      | 20  |

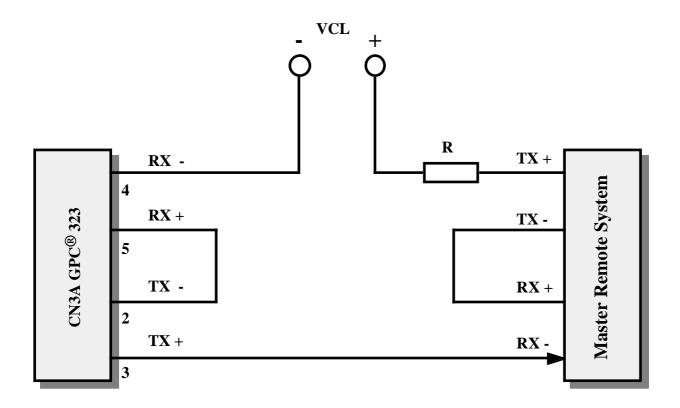

| FIGURE 12: SERIAL COMMUNICATION DIAGRAM                        | 21  |

| FIGURE 13: RS 232 PIN-OUT AND CONNECTION EXAMPLE               | 22  |

| FIGURE 14: RS 422 PIN-OUT AND CONNECTION EXAMPLE               | 22  |

| FIGURE 15: RS 485 PIN-OUT AND CONNECTION EXAMPLE               | 22  |

| FIGURE 16: RS 485 NETWORK CONNECTION EXAMPLE                   | 23  |

| FIGURE 17: CURRENT LOOP PIN-OUT AND 4 WIRES CONNECTION EXAMPLE | 24  |

| FIGURE 18: CURRENT LOOP PIN-OUT AND 2 WIRES CONNECTION EXAMPLE | 24  |

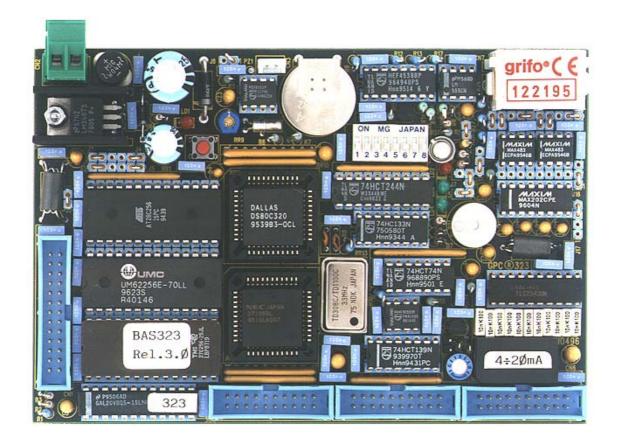

| Figure 19: Card photo                                          | 25  |

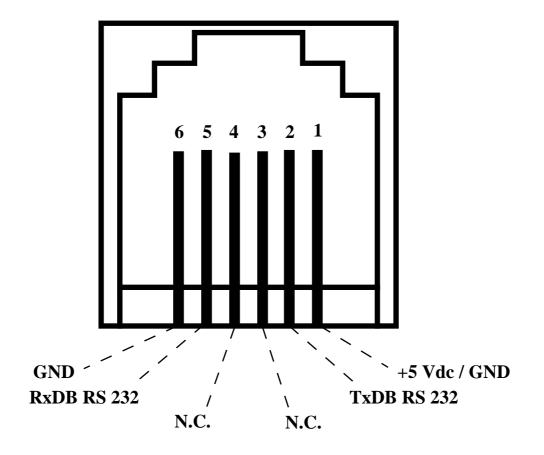

| FIGURE 20: CN3B - SERIAL LINE B CONNECTOR                      | 26  |

| FIGURE 21: CN2 - EXTERNAL BACK UP BATTERY CONNECTOR            | 27  |

| FIGURE 22: VISUAL FEEDBACK TABLE                               | 28  |

| FIGURE 23: JUMPERS SUMMARIZING TABLE                           | 32  |

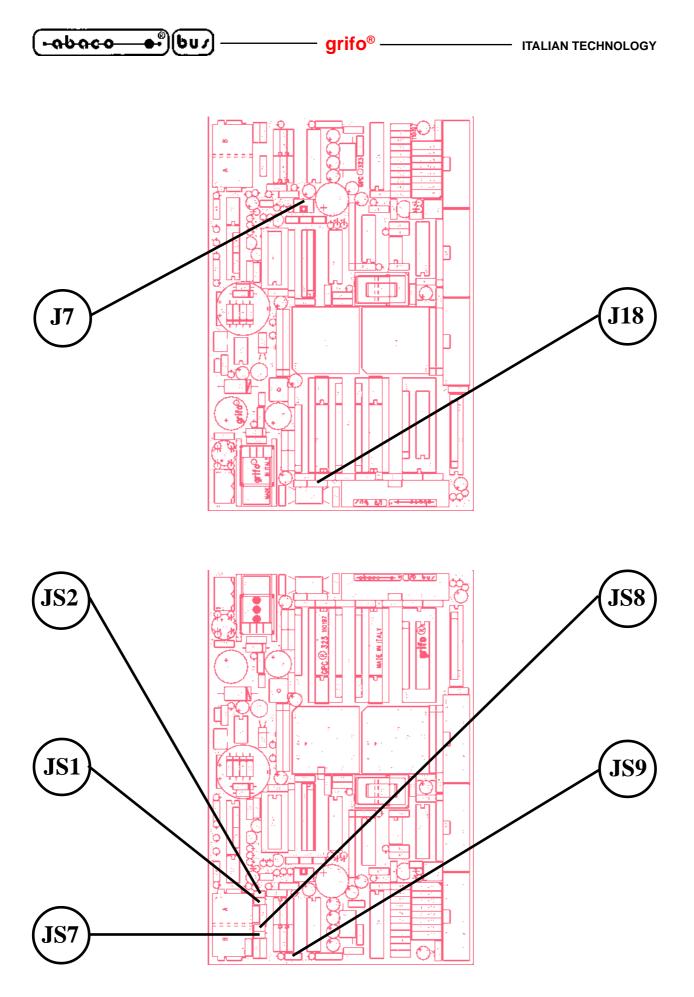

| FIGURE 24: COMPONENT SIDE JUMPERS LOCATION                     | 33  |

| FIGURE 25: 2 PINS JUMPERS TABLE                                | 34  |

| FIGURE 26: SOLDER SIDE JUMPERS LOCATION                        | 35  |

| FIGURE 27: 3 PINS JUMPERS TABLE                                | 36  |

| FIGURE 28: 6 PINS JUMPERS TABLE                                | 37  |

| FIGURE 29: MEMORY SELECTION TABLE                              | 39  |

| FIGURE 30: I/O ADDRESSES TABLE                                 | 42  |

| FIGURE 31: MEMORY CONFIGURATION 1 (ASM)                        | 43  |

| FIGURE 32: MEMORY CONFIGURATION 3 (ASM)                        | 44  |

| FIGURE 33: MEMORY CONFIGURATION 4 (BASIC)                      | 45  |

| FIGURE 34: Possible connections diagram                        | 55  |

| FIGURE A1: MEMORY JUMPERS LOCATIONA                            | -1  |

| FIGURE A2: SERIAL COMMUNICATION JUMPERS LOCATIONA              | -2  |

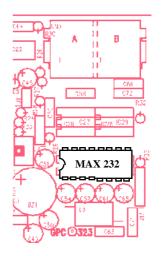

| FIGURE A3: SERIAL COMMUNICATION DRIVERS LOCATIONA              | -3  |

#### INTRODUCTION

The use of these devices has turned - IN EXCLUSIVE WAY - to specialized personnel.

The purpose of this handbook is to give the necessary information to the cognizant and sure use of the products. They are the result of a continual and systematic elaboration of data and technical tests saved and validated from the manufacturer, related to the inside modes of certainty and quality of the information.

The reported data are destined- IN EXCLUSIVE WAY- to specialized users, that can interact with the devices in safety conditions for the persons, for the machine and for the environment, impersonating an elementary diagnostic of breakdowns and of malfunction conditions by performing simple functional verify operations, in the height respect of the actual safety and health norms.

The informations for the installation, the assemblage, the dismantlement, the handling, the adjustment, the reparation and the contingent accessories, devices etc. installation are destined - and then executable - always and in exclusive way from specialized warned and educated personnel, or directly from the TECHNICAL AUTHORIZED ASSISTANCE, in the height respect of the manufacturer recommendations and the actual safety and health norms.

The devices can't be used outside a box. The user must always insert the cards in a container that rispect the actual safety normative. The protection of this container is not threshold to the only atmospheric agents, but specially to mechanic, electric, magnetic, etc. ones.

To be on good terms with the products, is necessary guarantee legibility and conservation of the manual, also for future references. In case of deterioration or more easily for technical updates, consult the AUTHORIZED TECHNICAL ASSISTANCE directly.

To prevent problems during card utilization, it is a good practice to read carefully all the informations of this manual. After this reading, the user can use the general index and the alphabetical index, respectly at the begining and at the end of the manual, to find information in a faster and more easy way.

#### CARD VERSION

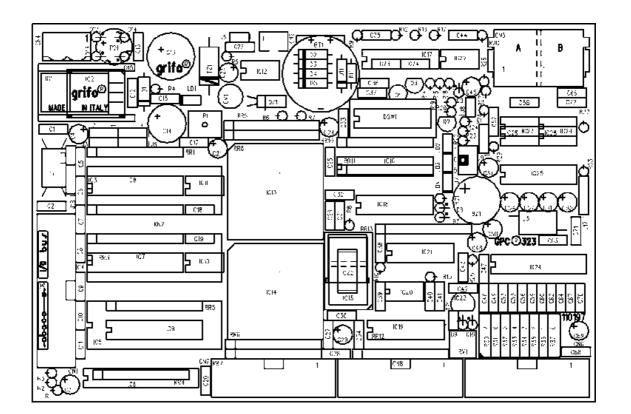

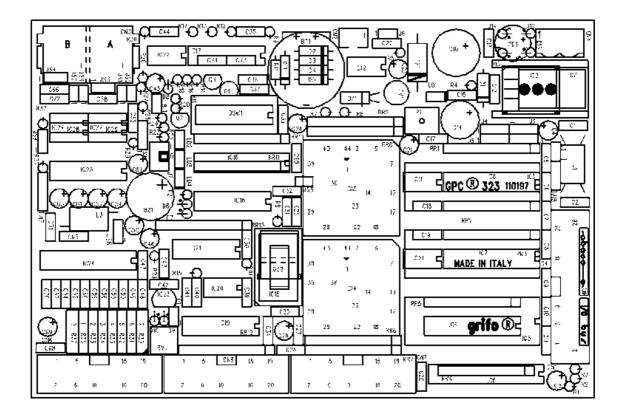

The present handbook is reported to the **GPC® 323** card release **110197** and later. The validity of the bring informations is subordinate to the number of the card release. The user must always verify the correct correspondence among the two denotations. On the card the release number is present in more points both board printed diagram (serigraph) and printed circuit (for example on the bottom right corner on the component side).

GENERAL FEATURES

**GPC® 323** is a powerful, low cost, controller module capable of operating in stand alone mode or as an intelligent peripheral, and/or remoted, in a wider telecontrol or aquisition network. The **GPC® 323** board is secured in a plastic mount for connection to **Omega** rails **DIN 46277-1** and **DIN 46277-3**, thereby dispensing with the need of rack and allowing a cheaper mounting direct to the electrical control panel. The most intresting feature of this board is the wide choice of microcontrollers it can mount. The board can be delivered with an 80C32 or the faster 80C320, the board general features remain the same but the performance vary remarkably according to the microcontroller installed. It is also possible to supply the board in many different ways, to solve any installation problem without no need to use expansive external power supplies. **GPC® 323** board is provided with a set of **Abaco®** standard connectors, allowing the User to connect it to any of the **BLOCK** I/O module or to third parts or User made interfaces to the field.

The Abaco<sup>®</sup> I/O BUS connector allows to drive directly the ZBR 324 and ZBT 324 cards and through ABB 03, ABB 05 and so on, it is possible to run all peripheral cards available on Abaco<sup>®</sup> BUS.

Many software development tools, both in Assembler and in high level languages, are available to allow the User to employ the GPC<sup>®</sup> 323 board as a development system of its own applcations. Noteworthy among these tools are the several C Compilers, the FORTH and the comfortable BASIC 323.

- Intelligent Abaco<sup>®</sup> BLOCK module, 4 serie, 100x50 mm size

- Optional plastic mount for connection to DIN 46277-1 and DIN 46277-3  $\Omega$  rails

- 14÷20 MHz 80C32 or 80C320 CPU, up to 96 KBytes maximum addressable memory

- Sockets for 32K EPROM, 32K RAM, 32K EEPROM, RAM or EPROM

- Back up circuitery for 32 KBytes RAM through internal lithium battery

- Optional RTC with 256 Bytes RAM backed through internal and external lithium battery

- Optional serial **EEPROM 512 to 2048 Bytes** size, maximum size is 1024 bytes if RTC is installed

- Eleven channels 12 Bits A/D Converter, +2,5V or  $0\div20$  mA full range,  $10\,\mu s$  conversion time

- 24 TTL I/O signals

- 4 status LEDs, 2 of which software programmable, and active BUZZER

- One Dip Switch with 5 pins software readable

- Three 16 bits Timer-Counter with Capture and Compare registers

- Watchdog

- Two RS 232 serial lines, one of which settable in RS 422, RS 485 or Current Loop

- 26 pins **Abaco**<sup>®</sup> I/O BUS expansion connector

- Two 20 pins I/O Abaco® standard connectors

- IDLE MODE or POWER DOWN MODE power saving features

- Optional on-board power supply or external +5Vdc power supply

- On board protection aganist voltage peaks by TransZorb<sup>TM</sup>

#### - Wide availability of software development tools as Monitor, Debugger, Assembler, GET 51 and Interpretated BASIC, BASIC Compiler, FORTH, C Compiler, HTC-51, HTC-51XA, PLM 51, PASCAL Compiler, etc.

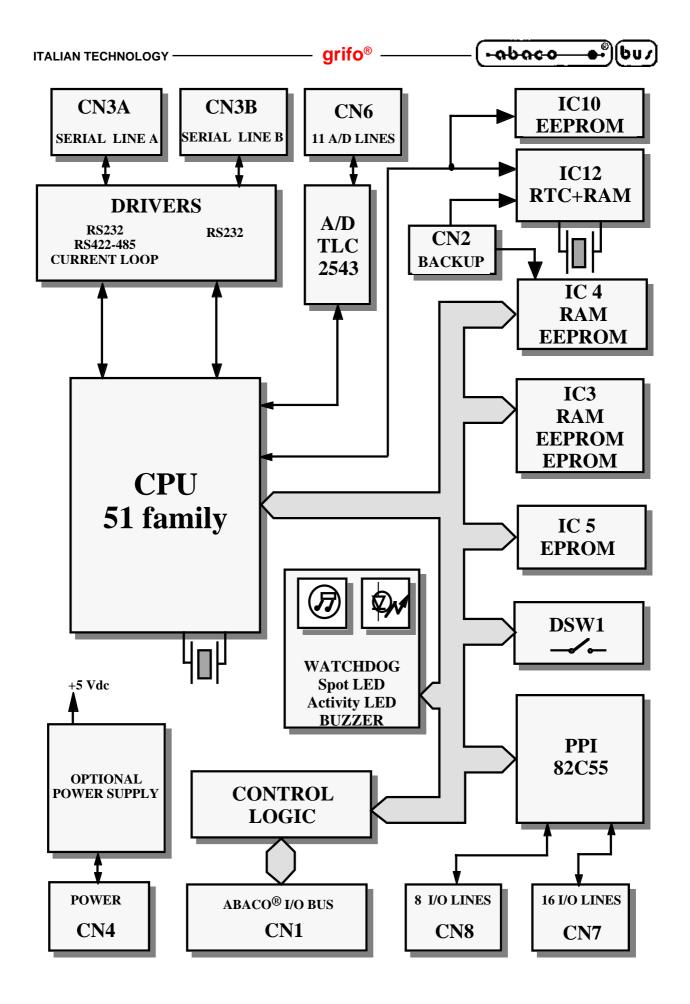

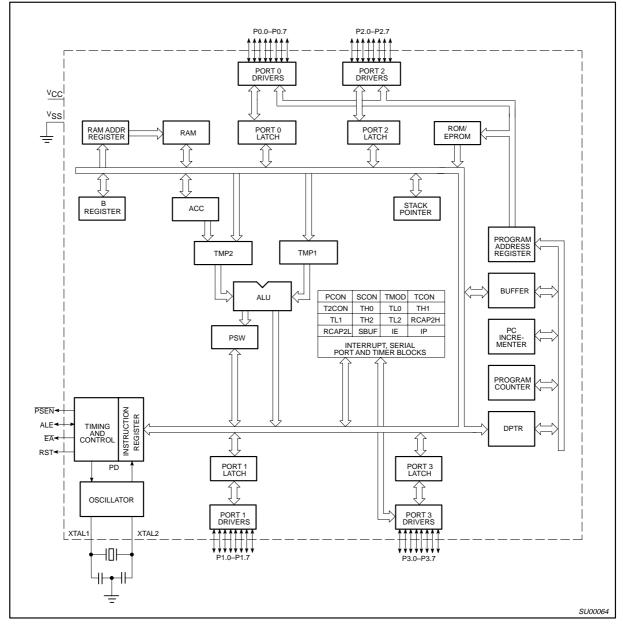

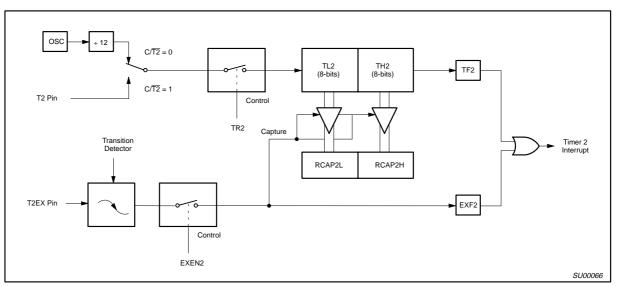

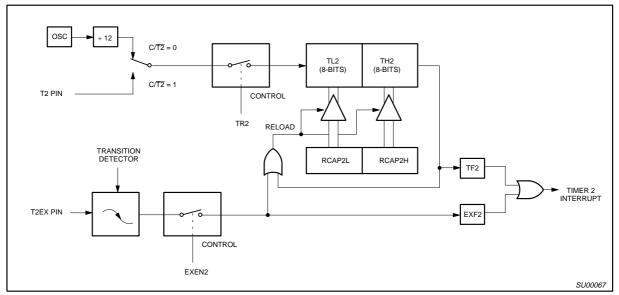

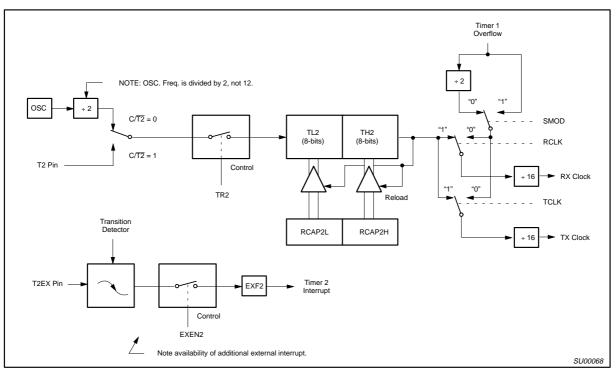

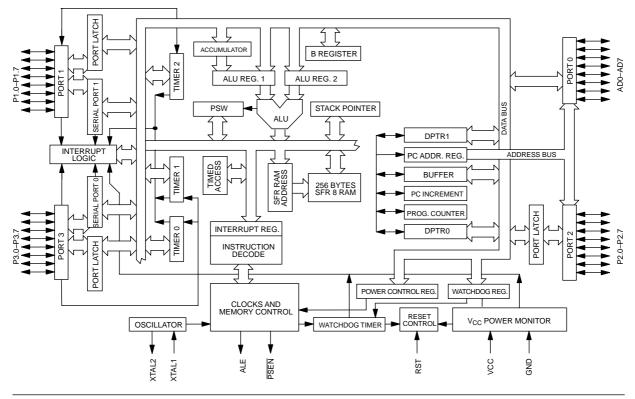

Here follows a description of the board's functional blocks, with an indication of the operations performed by each one. To easily locate these blocks and verify their connections pleare refer to figure 1.

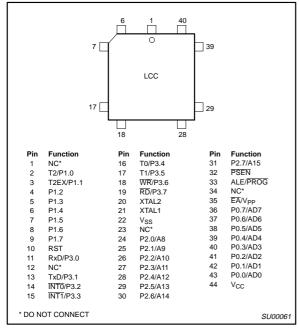

#### <u>CPU</u>

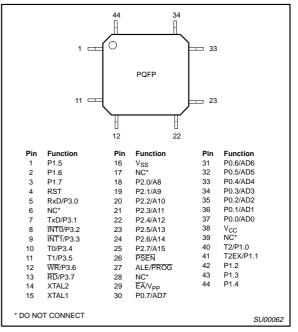

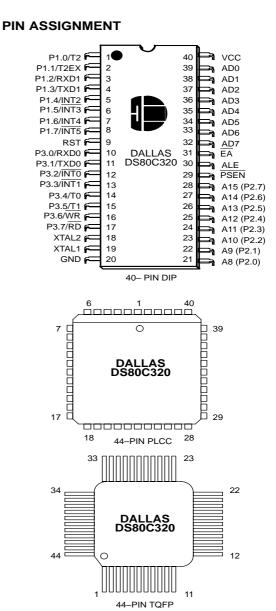

GPC<sup>®</sup> 323 board is designed to employ four differnt types of microcontroller: 80C32 manifactured by INTEL and other several manifacturers, 80C320 manifactured by DALLAS. These 8 and 16 bits CPU feature an extended instructions set, high speed of execution, efficient vectored interrupts management and iwide range of peripherals inside the CPU.

All paragraphs of this manual report a description of the features common to all microcontrollers distinguishing where needed.

Here follow the lists of the CPU features that the User is enabled to employ, according to the type of microcontroller installed:

| μP 80C32:  | - 8 bits CPU                                  |

|------------|-----------------------------------------------|

|            | - 256 Bytes of internal RAM                   |

|            | - One 8 bits I/O port                         |

|            | - 64K + 64K directly addressable memory       |

|            | - Three 16 bits Timer/Counters                |

|            | - 6 interrupt sources with 2 priority levels  |

|            | - 1 full duplex serial line                   |

|            |                                               |

| μP 80C320: | - 8 bits CPU                                  |

|            | - 256 Bytes of internal RAM                   |

|            | - One 8 bits I/O port                         |

|            | - 64K + 64K directly addressable memory       |

|            | - Three 16 bits Timer/Counters                |

|            | - 13 interrupt sources with 3 priority levels |

|            | - 2 full duplex serial lines                  |

- Power fail circuitry

- Watchdog timer

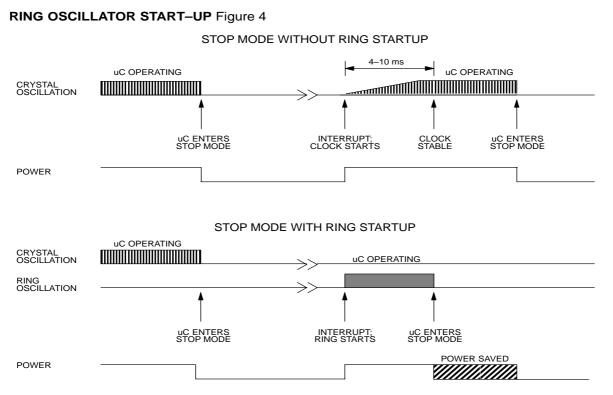

- Power down and idle mode management

For further informations about these components please refer to the manifacturer documentations.

#### **CLOCK**

On GPC<sup>®</sup> 323 board two different circuits provide the CPU clock frequence and the Real Time Clock frequence. This solution has been chosen because using a separate circuit to to generate the CPU clock allows to change it without having to make any other modification to the rest of the board. The Real Time Clock frequence is unique, its value is 32768 Hz, the CPU clock frequence may be picked from the following values:

14.7456 MHz or 22.1184 MHz μP 80C32: µP 80C320: 22.1184 MHz or 29.4912 MHz

Please remark that the CPU working frequence determinates the baud rate for the serial communication line/s.

#### **POWER SUPPLY**

The **GPC® 323** board can be optionally provided with the power supply section capable to generate the unique +5 Vdc voltage needed to supply the board. Shold the supply section be absent, the +5Vdc voltage is the only one needed to supply the board, otherwise two different types of supply sections are available: linear supply section, which requires an alternate input voltage in the range 6÷12 Vac; switching supply section, which requires an alternate input voltage in the range 15÷24 Vac (for further informations please refer to the paragraph "SUPPLY VOLTAGES". The supply voltage can be supplied through proper standard connectors fast and easy to use. The power supply circuit is designed for reducing the consumption (the microprocessor power down and idle modes are available) and for increasing the electrical noise immunity.

arifo®

The type of supply cannot be changed by the User so it must be specified in the order.

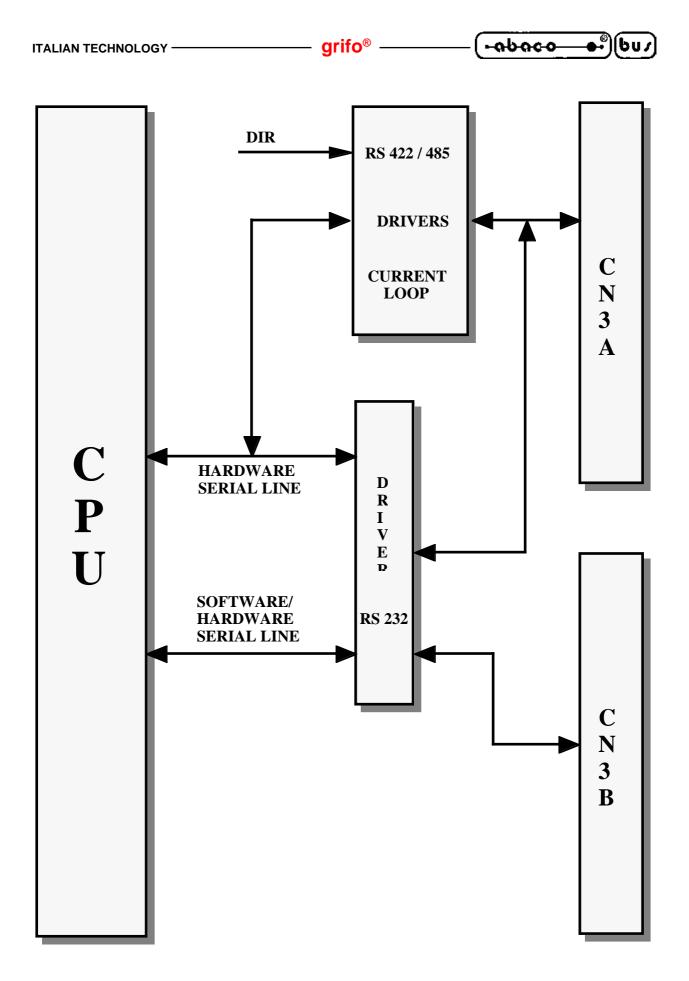

#### **SERIAL COMMUNICATION**

**GPC® 323** board is always provided with an hardware serial communication line (called serial A) which is completely software settable for protocol and for speed. These settings are performed programming the ASP inside the microprocessor, so for further informations, please refer to the manifacturer documentation or to appendixes of this manual. The board also provides a second serial communication line (called seiral B) made as follows:

| μP 80C32:  | software serial port managed through two microprocessor I/O signals  |

|------------|----------------------------------------------------------------------|

| μP 80C320: | hardware serial port managed through microprocessor inside registers |

The User can set by software also protocol and speed of serial B, in case of software serial line the software itself will have to perform all the settings (for further informations please refer to the software tools manuals or contact **grifo**<sup>®</sup>).

The serial line B is always buffered as RS 232, while for serial line A by hardware it is possible to select, through some on board jumpers, the electric communication protocol. In detail, it can be buffered as: RS 232, passive Current Loop or RS 422-485; in this last cases also full duplex or half duplex are programmable.

FIGURE 1: BLOCK DIAGRAM

**GPC® 323 Rel. 5.20** — Page 5

#### **MEMORY DEVICES**

On the card can be monted 98K bytes plus 256 bytes of memory divided with a maximum of 32K EPROM, 32K RAM or EEPROM, 32K RAM or EEPROM or EPROM, 256 bytes serial RAM+RTC and 2K serial EEPROM. The **GPC® 323** memory configuration must be chosen considering the application to realize or the specific requirements of the user. Normally the card is equipped with 32K bytes of RAM and all different configurations must be specified by the User, at the moment of the order.

arifo®

With the on board back up circuit there is the possibility to keep 32K plus 256 bytes RAM, also when power supply is failed; in this way the card is always able to maintain parameters, logged data, system status and configuration, etc. without using expensive external UPS. The back up circuit is supplied by a on board lithium battery or an external battery to be connected to a specific connector. Should the amount of backed memory result insufficent, it is possible to add backed RAM modules and/or EEPROM.

The memory module to install in IC12 can also be provided with a Real Time Clock capable to manage through software time (hours, minutes, seconds) and date (day, month, year, day of week). The memory resources mapping is performed by a specific circuitry that allocates the memory devices inside the microprocessor addressing space; this control logic also provides to manage automatically the different memory mappings provided to suite the needs of the several software packages available for **GPC<sup>®</sup> 323** board.

For further informations please refer to the chapter "HARDWARE DESCRIPTION" and "PERIPHERALS SOFTWARE DESCRIPTION".

For further informations about memory configuration, sockets description and jumpers connection, please refer to paragraph "MEMORY SELECTION".

— grifo<sup>®</sup> —

-**●•**)(bu∕

-abaco

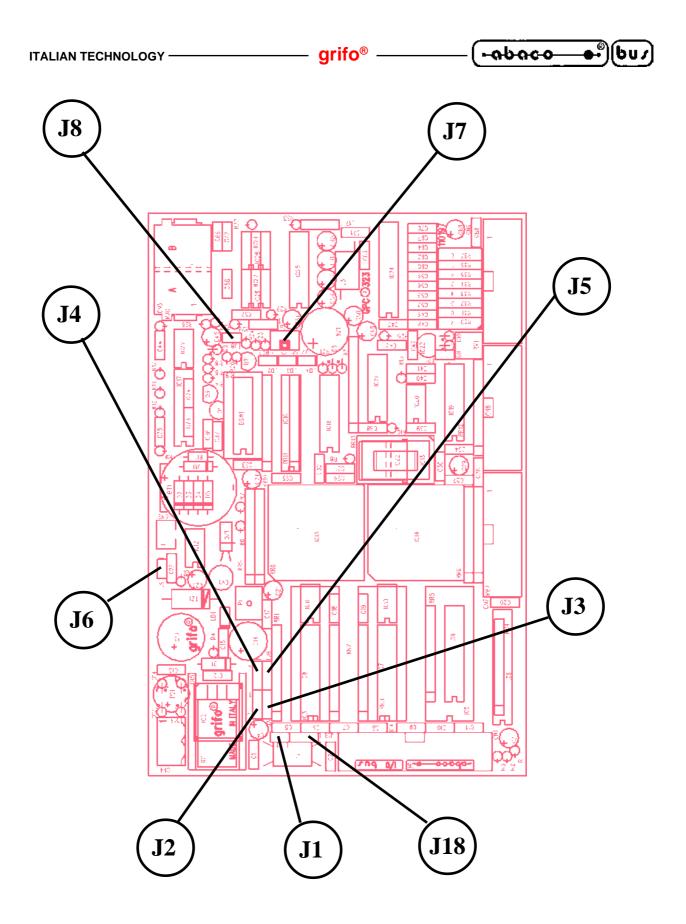

FIGURE 2: COMPONENTS MAP

#### **ON BOARD PERIPHERAL DEVICES**

**GPC<sup>®</sup> 323** board has been designed to solve several problems of industrial automation control, so it has been provided with peripheral devices that perform an interface to the external world. In detail:

- arifo®

- A/D converter: this peripheral can acquire 11 channels with a maximun resolution of 12 bits. By software it is possible to decide which channels to employ, to start and to stop the acquisition, etc., through a synchronous communication to the device. By means to simplify the management of this device some software packages provide utility procedures that are capable to manage all its parts. The connectable analog signals are variable voltage signals in the range 0+2.49V (optional 0+5V to specify in the order) or current signals in the range 0+20 mA. This device is optional and must be explicitally requested in the order.

- Watchdog: astable section not microprocessor inside with about 1.5 s of intervent time. The retrigger is completely software performed thorugh the access to opportune registers located in the microprocessor addressing space and gives to the board an extermly high degree of safety. The intervent time can be changed on request of the User by interventing on specific RC networks (in case of need please contact **grifo**<sup>®</sup>). Should the board use microprocessors provided with a watch dog section inside the User could take advantage of two separated circuitry providing different characteristics, so the safety degree of the board would increase.

- **Board configuration**: to make the board and the applications program developed for it easier to configure an 8 pins dip switch has been installed. This dip switch has a triple configuration purpose:to select memory configuration, to select the RUN/DEBUG modality and to configure the management software. The possibility to read by software the status of some switches allows the User the chance to manage several working conditions through an unique program without no need to employ more input signals (characteristic applications are: language selection, program parameter determination, working modalities selection, etc.). On **GPC® 323** board two activity LEDs have been installed, these LEDs are software managed and the User may employ them to provide visual feedback about the syztem status.

- **Real Time Clock**: the backed RAM module to install on IC12 can be provided with a complete Real Time Clock module capable to manage hour, minutes, seconds, day of month, month, year and day of week as a stand alone device. This component is optional and installed only if explicitally requested in the order.

- Serial EEPROM: the serial EEPROM module to install on IC10 is essential to the User who needs to keep informations in memory also when power supply fails without using the backed RAM module, obtaining this way an extremly high degree of safety for data integrity. Size of this module can vary in the range 521÷2048 bytes, it is optional and must be explicitally specified in the order.

- **Buzzer**: **GPC**<sup>®</sup> **323** board features a capacitive buzzer capable to produce a constant sound, driven by a circuitry that can be software enabled and/or disabled through the cotrol logic, that can be used to generate acoustic alerts, sound feedback, etc.

|  | grifo <sup>®</sup> ——— | (-abaco• | (bu/) |

|--|------------------------|----------|-------|

|--|------------------------|----------|-------|

- **PPI 82C55**: this peripheral can manage three 8 bits parallel ports performing 24 TTL level I/O signals whose directionality is byte-level software settable. These I/O signals provide the **GPC® 323** board more employ possibilities (for example the management of non intelligent peripherals, interfaces, etc.) also in applications where the communcation handshake must be completely software managed. PPI 82C55 can be completely programmed through four registers located in the CPU addressing space.

For further informations about the above described peripherals devices, please refer to the manifacturer documentation or to appendix A of this manual.

#### <u>ABACO® I/O BUS</u>

One of the most important features of **GPC® 323** board is its possibility to be interfaced to industrial **ABACO®** I/O BUS .Thanks to this standard connector, the card can be connected to some of the numerous **grifo®** boards, both intelligent and not. For example the user can directly use cards for analog signals acquisition, cards for analog signals generation (D/A), cards for digital I/O signals management, cards with timers and counters, cards for temperature controls, etc. also custom boards designed to satisfy specific needs of the end user.

Using **ABB 03** or **ABB 05** mother boards it is possible manage even all the BUS **ABACO**<sup>®</sup> single EURO cards. So **GPC**<sup>®</sup> **884** becomes the right component for each industrial automation system, in fact **ABACO**<sup>®</sup> I/O BUS makes the card easily expandable with the best price/performance ratio.

#### **CONTROL LOGIC**

Registers of all the peripherals installed on GPC<sup>®</sup> 323 board are mapped through a specific control logic circuit that maps them inside the microprocessor addressing space. For further informations please refer to the paragraph "I/O MAPPING".

#### **RESET KEY**

**GPC® 323** board features a comfortable reset key that, when pushed, restarts the board from a general reset condition. The main purpose of this key is to exit from inifinite loop conditions, useful especially during the debug phae or to warrant a special starting status.

| -abaco- | _ <b>●•</b> )(bu/ |

|---------|-------------------|

TECHINICAL FEATURES

#### **GENERAL FEATURES**

| <b>Board Resources</b> :<br>(except µP resources) | <ul> <li>24 TTL programmable Input/Output signals <ol> <li>RS 232 or RS 422-485 or Current Loop bidirectional line</li> <li>RS 232 bidirectional line</li> <li>Hardware Watchdog</li> </ol> </li> <li>11 A/D converter signals <ol> <li>Reset key</li> <li>Real Time Clock</li> <li>Software manageable LEDs</li> <li>Eight pins Dip Switch (5 software readables)</li> <li>Abaco<sup>®</sup> I/O BUS expansion connector</li> </ol> </li> </ul> |                                                                                                                                                                      |  |

|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Addressable Memory:                               | IC 5:<br>IC 4:<br>IC 3:<br>IC 10:<br>IC 12:                                                                                                                                                                                                                                                                                                                                                                                                      | EPROM 32K x 8<br>RAM/EEPROM from 8K x 8 to 32K x 8<br>RAM/EEPROM/EPROM from 8K x 8 to 32K x 8<br>Serial EEPROM from 512 byte to 2048 byte<br>Serial RAM+RTC 256 byte |  |

| CPU:                                              | INTEL 80                                                                                                                                                                                                                                                                                                                                                                                                                                         | C32; DALLAS 80C320                                                                                                                                                   |  |

| Clock Frequence:                                  | μΡ 80C32<br>μΡ 80C32                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                      |  |

| A/D Resolution:                                   | 12 bits                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                      |  |

| A/D Conversion Time:                              | 10 µs                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                      |  |

| PHYSICAL FEATURES                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                      |  |

| Size:              | 100 x 149 mm                                                   |                                                                                                                                                                                                                                                                                                                                                                          |  |

|--------------------|----------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Weight:            | 170 g (complete configuration)                                 |                                                                                                                                                                                                                                                                                                                                                                          |  |

| Connectors:        | CN1:<br>CN2:<br>CN3A:<br>CN3B:<br>CN4:<br>CN6:<br>CN7:<br>CN8: | <ul> <li>26 pins, male, vertical, low profile connector</li> <li>2 pins, male, vertical, low profile connector</li> <li>6 pins, Plug, female</li> <li>2 pins screw terminal connector</li> <li>20 pins, male, vertical, low profile connector</li> <li>20 pins, male, vertical, low profile connector</li> <li>20 pins, male, vertical, low profile connector</li> </ul> |  |

| Temperature Range: | from 0 to                                                      | 70 centigrad degreeses                                                                                                                                                                                                                                                                                                                                                   |  |

|                                                   | grifc                                                  | ° °                                                                                                 | - bus       |

|---------------------------------------------------|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-------------|

| <b>Reative Humidity</b> :                         | 20% op tp 90% (without condense)                       |                                                                                                     |             |

| Watchdog Intervent Time:                          | 1.5 s                                                  |                                                                                                     |             |

| ELECTRIC FEATURES                                 |                                                        |                                                                                                     |             |

| Power Supply:                                     | 5 Vdc<br>6 ÷ 12 Vac<br>15 ÷ 24 Vac                     | (without power supply section)<br>(linear power supply section)<br>(switching power supply section) | *           |

| Consumption on 5 Vdc:                             | μΡ 80C32:<br>μΡ 80C320:                                | 100÷300 mA<br>200÷400 mA                                                                            |             |

| Current provided on +5 Vdc<br>for external loads: | μΡ 80C32:<br>μΡ 80C320:                                | 300÷100 mA (switching)<br>900÷700 mA (linear)<br>200÷0 mA (switching)<br>800÷600 mA (linear)        | *<br>*<br>* |

| External Back up Battery:                         | 3.6÷5 Vdc                                              |                                                                                                     |             |

| Back up Current:                                  | 15 μΑ                                                  |                                                                                                     |             |

| Analog Inputs Voltage:                            | 0÷2.49 Vcc or 0÷5 Vcc                                  |                                                                                                     |             |

| Analog Inputs Current:                            | 0÷20 mA                                                |                                                                                                     |             |

| Analog Inputs Impedance:                          | 1 KΩ                                                   |                                                                                                     |             |

| RS 422-485 Termination Net:                       | Line terminatio<br>Positive pull up<br>Negative pull d |                                                                                                     |             |

\* Data here reported are referred to a 20 centigrad degreeeses environmental temperature (for further informations please refer to the paragraph "SUPPLY VOLTAGES").

20

#### INSTALLATION

In this chapter there are the information for a right installation and correct use of the card. The user can find the location and functions of each connectors, trimmers, LEDs, jumpers and some explanatory diagrams.

- grifo® -

#### **CONNECTIONS**

The **GPC®323** module has 7 connectors that can be linkeded to other devices or directly to the field, according to system requirements. In this paragraph there are connectors pin outs, a short signals description (including the signals direction) and connectors location (see figure 8), plus some figures that describe how the interface signals are connected on the card.

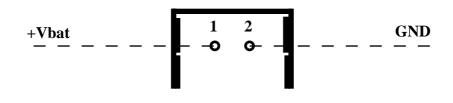

#### **CN 4 - POWER SUPPLY CONNECTOR**

CN4 is a 2 pins screw terminal connector. The board supply voltage must be provided through this connector. When using the board without any power supply section, the +5 Vdc must be provided through pin 26 (+Vdc) and pin 25 (GND) of CN1.

FIGURE 3: CN4 - POWER SUPPLY CONNECTOR

Signals description:

**15÷24 Vac / 6÷12 Vac** = I - 15÷24 Vac power supply signals (switching supply section) I - 6÷12 Vac power supply signals (linear supply section)

#### – grifo<sup>®</sup> -

#### **CN1 - ABACO® I/O BUS CONNECTOR**

CN1 is a 26 pins, male, vertical, low profile connector.

Through CN1 the card can be connected to external expansion modules developed by the user or to the numerous **grifo**<sup>®</sup> boards, both intelligent and not. All this connector's signals are at TTL level and follow the **ABACO**<sup>®</sup> **I/O BUS** standard.

| <u>D0</u>    | -1               | 2<br><b>o</b>    | <u>D1</u>      |

|--------------|------------------|------------------|----------------|

| <u>D2</u>    | $-\frac{3}{0}$   | 4<br>0           | <u>D3</u>      |

| <u>D4</u>    | 5<br><b>0</b>    | 6<br><b>0</b>    | <u>D5</u>      |

| <u>D6</u>    | - 7              | 8<br><b>o</b>    | <u>D7</u>      |

| <u>A0</u>    | 9<br>0           | 10<br><b>o</b>   | A1             |

| <u>A2</u>    |                  | 12<br><b>o</b>   | <u>A3</u>      |

| <u>A</u> 4   |                  | 14<br>o          | <u>A5</u>      |

| <u>A6</u>    |                  | 16<br><b>0</b>   | A7             |

| <u>/WR</u>   | 17               | 18<br>0          | <u>/RD</u>     |

| <u>/IORQ</u> | 19<br>0          | 20<br><b>o</b>   | <u>/RESET</u>  |

| <u>N.C.</u>  | 21<br>- <b>O</b> | 22<br>o          | <u>N.C.</u>    |

| <u>/INT</u>  | $-\frac{23}{0}$  | 24<br>o          | / <u>NMI</u>   |

| <u>GND</u>   | 25<br><b>0</b>   | 26<br><b>0</b> - | + <u>5</u> Vdc |

|              |                  |                  |                |

|              |                  | OB TO T          |                |

Signals description;

| A0-A7    | =          | 0   | - Address BUS.                                  |

|----------|------------|-----|-------------------------------------------------|

| D0-D7    | =          | I/O | - Data BUS.                                     |

| /INT BUS | 5 =        | Ι   | - Interrupt request (open collector type).      |

| /NMI BU  | <b>S</b> = | Ι   | - Non maskable interrupt (open collector type). |

| /IORQ    | =          | 0   | - Input output request.                         |

| /RD      | =          | 0   | - Read cycle status.                            |

| /WR      | =          | 0   | - Write cycle status.                           |

| /RESET   | =          | 0   | - Reset.                                        |

| +5 Vdc   | =          | I/O | - +5 Vdc power supply.                          |

| GND      | =          |     | - Ground signal.                                |

| N.C.     | =          |     | - Not connected                                 |

#### CN7 - PPI 82C55 PORT A AND C I/O CONNECTOR

CN7 is a 20 pins, male, vertical, low profile connector, 2.54 mm pitch. Through CN1 two of the three programmable peripheral PPI 82C55 8 bits parallel ports are conected to external world. All this connector's signals are at TTL level and follow the **ABACO® I/O BUS** standard.

| <u>PA.1</u> | $-\mathbf{o}^1$    | 2<br><b>o</b>      | <u>PA.0</u> |

|-------------|--------------------|--------------------|-------------|

| <u>PA.3</u> | $-\frac{3}{0}$     | 4<br>0             | <u>PA.2</u> |

| <u>PA.5</u> | $-{\bf 0}^{5}$     | 6<br><b>0</b>      | <u>PA.4</u> |

| <u>PA.7</u> | <b>7</b>           | 8<br><b>o</b>      | <u>PA.6</u> |

| <u>PC.6</u> | -]-ø               | 10<br><b>o</b>     | <u>PC.7</u> |

| <u>PC.4</u> |                    | 12<br><b>o</b>     | <u>PC.5</u> |

| <u>PC.2</u> |                    | 14<br><b>o</b>     | <u>PC.3</u> |

| <u>PC.0</u> | 15<br>- <b>O</b>   | 16<br><b>0</b> – - | <u>PC.1</u> |

| <u>GND</u>  | $-\frac{17}{0}$    | 18<br><b>o</b>     | +5 Vdc      |

| <u>N.C.</u> | - 19<br>- <b>o</b> | 20<br><b>o</b>     | <u>N.C.</u> |

|             |                    |                    |             |

#### FIGURE 5: CN7 - PPI 82C55 PORT A AND C I/O CONNECTOR

Signals description:

| PA.n   | = | I/O | - | PPI 82C55 port A n-th digital signal |

|--------|---|-----|---|--------------------------------------|

| PC.n   | = | I/O | - | PPI 82C55 port C n-th digital signal |

| GND    | = |     | - | Ground signal                        |

| +5 Vdc | = | Ο   | - | +5 Vcc signal                        |

| N.C.   | = |     | - | Not connected                        |

Remarkable is the possibility to connect directly through CN7 a set of interfaces designed to solve several typical problems of industrial automation. We especially would want to remark the simplicity of installation and software management of **QTP 24P**, **KDL x24**, **KDF 224**, etc., that are also supported by high level programming languages. For further informations please refer to the paragraph "OPERATOR INTERFACES".

FIGURE 6: I/O SIGNALS CONNECTION DIAGRAM

#### CN8 - PPI 82C55 PORT B I/O CONNECTOR

CN8 is a 20 pins, male, vertical, low profile connector, 2.54 mm pitch. Through CN8 one of the three programmable peripheral PPI 82C55 8 bits parallel ports are conected to external world. All this connector's signals are at TTL level and follow the **ABACO® I/O BUS** standard.

|             | <b></b>            |                    | 1 |                  |

|-------------|--------------------|--------------------|---|------------------|

| <u>PB.1</u> | $-0^1$             | 2<br><b>o</b>      |   | <br><u>PB.0</u>  |

| <u>PB.3</u> | $-\frac{3}{0}$     | 4<br><b>o</b>      |   | <br><u>PB.2</u>  |

| <u>PB.5</u> | $-5^{5}$           | 6<br>0             |   | <br><u> PB.4</u> |

| <u>PB.7</u> | -7 <b>0</b>        | 8<br><b>o</b>      |   | <br><u> PB.6</u> |

| <u>N.C.</u> | -]-°               | 10<br>O— -         |   | <br><u> </u>     |

| <u>N.C.</u> | -11<br>-0          | 12<br><b>o</b>     |   | <br><u>N.C.</u>  |

| <u>N.C.</u> |                    | 14<br>o            |   | <br><u>N.C.</u>  |

| <u>N.C.</u> | 15<br>- <b>0</b>   | 16<br><b>0</b>     |   | <br><u>N.C.</u>  |

| <u>GND</u>  | -17<br>- <b>0</b>  | 18<br><b>0</b> – - |   | <br>-+5Vdc       |

| <u>N.C.</u> | - 19<br>- <b>o</b> | 20<br>o            |   | <br><u>N.C</u> . |

|             |                    |                    |   |                  |

FIGURE 7: CN8 - PPI 82C55 PORT B I/O CONNECTOR

Signals description:

| PB.n   | = | I/O | - | PPI 82C55 port B n-th digital signal |

|--------|---|-----|---|--------------------------------------|

| GND    | = |     | - | Ground signal                        |

| +5 Vdc | = | 0   | - | +5 Vcc signal                        |

| N.C.   | = |     | - | Not connected                        |

0

FIGURE 8: LEDS, CONNECTORS, DIP SWITCH, ETC. LOCATION

#### **CN6 - A/D CONVERTER INPUT CONNECTOR**

CN6 is a 20 pins, male, vertical, low profile connector, 2.54 mm pitch. Through CN6 the 11 A/D converter section input signals interface to the external world.

This connector accepts voltage analog signals  $(0 \div 2.49 \text{ Vcc})$  or current analog signals  $(0 \div 20 \text{ mA})$  and follow the **A/D ABACO**<sup>®</sup> standard.

| 1 2<br><b>o o</b>   | ADC9                                                 |

|---------------------|------------------------------------------------------|

| 3 4<br><b>o o</b>   | ADC10                                                |

| 5 6<br><b>0 0</b>   |                                                      |

| 7 8<br><b>o o</b>   | ADC1                                                 |

| 9 10<br><b>o o</b>  | ADC2                                                 |

| 11 12<br><b>0 0</b> | ADC3                                                 |

| 13 14<br>• • •      | <u>ADC4</u>                                          |

| 15 16<br><b>0 0</b> | ADC5                                                 |

| 17 18<br>O O        | <u>ADC6</u>                                          |

| 19 20<br>o o        | <u>ADC7</u>                                          |

|                     |                                                      |

|                     | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ |

#### FIGURE 9: CN6 - A/D CONVERTER INPUT CONNECTOR

Signals description:

| ADCn   | = | Ι | - | A/D converter n-th channel analog input |

|--------|---|---|---|-----------------------------------------|

| GND    | = |   | - | Digital ground signal                   |

| AGND   | = |   | - | Analog ground signal                    |

| +5 Vdc | = | Ο | - | +5 Vcc signal                           |

\_\_\_\_\_(•••b••c••\_••)(bu /

FIGURE 10: A/D CONVERTER INPUT BLOCK DIAGRAM

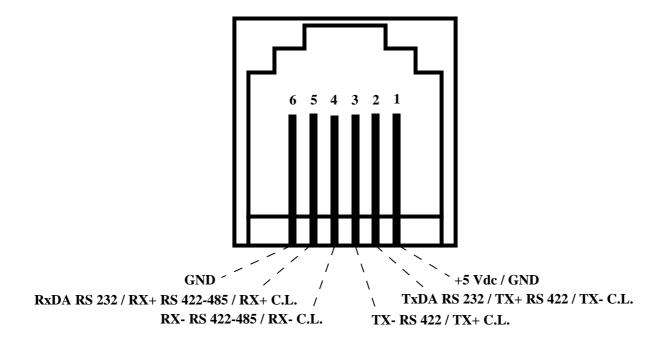

#### **CN3A - SERIAL LINE A CONNECTOR**

CN3A is a 6 pins, female PLUG connector for serial communication.

Placing of the signal has been designed to reduce interference and electrical noise and to simplify connections with other systems, while the electric protocol follows the CCITT normative.

| Legenda:          |     |   |   |                                                                                       |

|-------------------|-----|---|---|---------------------------------------------------------------------------------------|

| RX- RS 422-48     | 5 = | Ι | - | Receive Data Negative: negative signal for RS 422-485 serial differential receive     |

| RX+ RS 422-48     | 85= | Ι | - | Receive Data Positive: positive signal for RS 422-485 serial differential receive     |

| TX- RS 422        | =   | 0 | - | Transmit Data Negative: negative signal for RS 422-485 serial differential transmit   |

| TX+ RS 422        | =   | 0 | - | Transmit Data Positive: positive signal for RS 422-485 serial differential transmit   |

| <b>RxD RS 232</b> | =   | Ι | - | Receive Data: RS 232 Receive Data signal                                              |

| <b>TxD RS 232</b> | =   | 0 | - | Transmit Data: RS 232 Transmit Data signal                                            |

| RX- C.L.          | =   | Ι | - | Receive Data Negative: negative signal for Current Loop serial differential receive   |

| RX+ C.L.          | =   | Ι | - | Receive Data Positive: positive signal for Current Loop serial differential receive   |

| TX- C.L.          | =   | 0 | - | Transmit Data Negative: negative signal for Current Loop serial differential transmit |

| TX+ C.L.          | =   | 0 | - | Transmit Data Positive: positive signal for Current Loop serial differential transmit |

| +5 Vdc/GND        | =   | Ι |   | +5 Vcc or ground signal                                                               |

| GND               | =   |   |   | Ground signal                                                                         |

FIGURE 12: SERIAL COMMUNICATION DIAGRAM

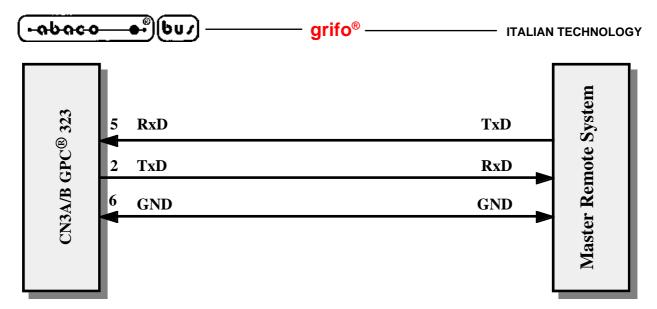

FIGURE 13: RS 232 PIN-OUT AND CONNECTION EXAMPLE

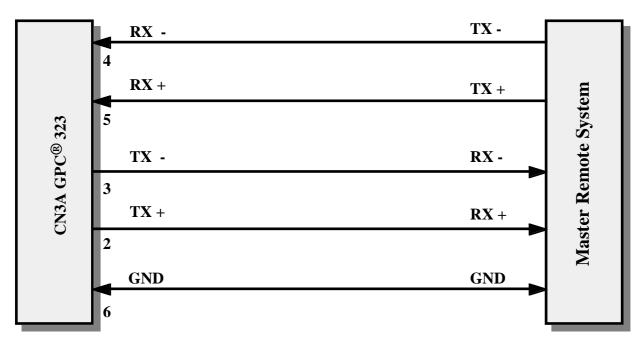

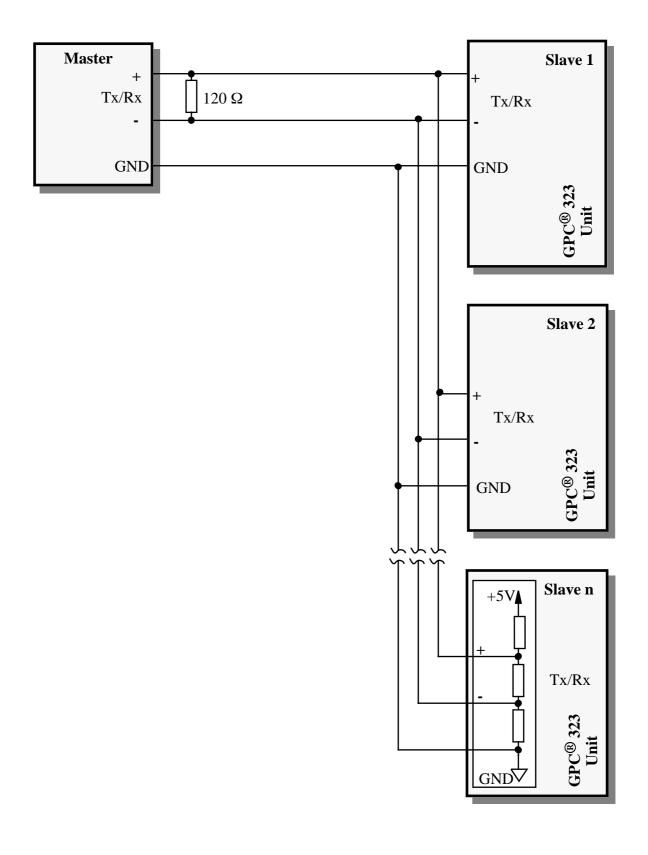

FIGURE 14: RS 422 PIN-OUT AND CONNECTION EXAMPLE

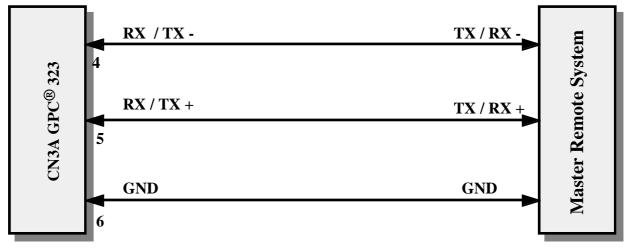

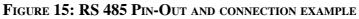

FIGURE 16: RS 485 NETWORK CONNECTION EXAMPLE

FIGURE 17: CURRENT LOOP PIN-OUT AND 4 WIRES CONNECTION EXAMPLE

FIGURE 18: CURRENT LOOP PIN-OUT AND 2 WIRES CONNECTION EXAMPLE

FIGURE 19: CARD PHOTO

#### **CN3B - SERIAL LINE B CONNECTOR**

CN3B is a 6 pins, female PLUG connector for serial communication.

Placing of the signal has been designed to reduce interference and electrical noise and to simplify connections with other systems, while the electric protocol follows the CCITT normative.

Signals description:

| RxDB RS 232 | = | Ι | - | Receive Data: RS 232 Receive Data signal   |

|-------------|---|---|---|--------------------------------------------|

| TxDB RS 232 | = | 0 | - | Transmit Data: RS 232 Transmit Data signal |

| +5 Vdc/GND  | = | Ι |   | +5 Vcc or ground signal                    |

| GND         | = |   |   | Ground signal                              |

| N.C.        | = |   | - | Not connected                              |

#### **CN2 - EXTERNAL BACK UP BATTERY CONNECTOR**

CN2 is a 2 pins, male, vertical, low profile connector, 2.54 mm pitch. Through CN2 the external back up battery that keeps on board RAM data integer and feeds the optional Real Time Clock also when power supply fails must be connected (for further informations please refer to the paragraph "BACK UP").

FIGURE 21: CN2 - EXTERNAL BACK UP BATTERY CONNECTOR

Signals description:

| +Vbat | = | Ι | - | Positive terminal of external back up battery |

|-------|---|---|---|-----------------------------------------------|

| GND   | = |   | - | Negative terminal of external back up battery |

#### **OPERATOR INTERFACES**

Through CN7 (I/O Abaco<sup>®</sup> standard connector) GPC<sup>®</sup> 323 board can be connected to several grifo<sup>®</sup> cards featuring the same pin out. Especially remarkable is the possibility to connect directly modules as QTP 24P, KDL x24, KDF 224, etc. that may solve any operator interfacement problems. These modules are provided with the resouces (alphanumeric display, matrix keycoard and LEDs) essential to manage an high level human-to-machine interfacement at a small distance to GPC<sup>®</sup> 323. To install one of these interfaces the User needs just a 20 pins flat cable, which transports both the signals and the interface power supply, while the software management can be easily performed through the procedures provided by any software packages suitable to GPC<sup>®</sup> 323. These procedures for most of the software packages are "software drivers" added to the programming language, that allow to use directly the "console management instructions" provided by the language itself. For further informations please refer to the chapter "EXTERNAL CARDS" and to the documentation of the software development tool being used.

#### VISUAL FEEDBACK

**GPC® 323** board is provided with four LEDs to signal status conditions, as described in the following table:

| LED | COLOUR | FUNCTION                                             |

|-----|--------|------------------------------------------------------|

| LD1 | Red    | It signals the presence of +5 Vcc power supply.      |

| LD2 | Red    | It signals the external watchdog circuitry activity. |

| LD3 | Green  | Software managed timed activity LED (spot).          |

| LD4 | Green  | Software managed activity LED.                       |

#### FIGURE 22: VISUAL FEEDBACK TABLE

The main purpose of these LEDs is to give a visual indication of the board status, making easier the operations of system working verify. To easily locate these LEDs on the board, please refer to figure 8.

#### **I/O CONNECTION**

To prevent possible connecting problems between **GPC® 323** and the external systems, the user has to read carefully the information of the previous paragraphs and he must follow these instrunctions:

- For RS 232,RS 422, Current Loop or RS 485 communication signals the User must follow the standard rules of these protocols.

- For all TTL signals the user must follow the rules of this electric standard. The connected digital signal must be always referred to card digital ground (GND). For TTL signals, the 0 Vdc level corresponds to logic state "0", while 5Vdc level corrisponds to logic state "1".

- The analog inputs (A/D section) must be connected to low impedance signals in the following ranges: 0÷2,490 V or 0÷5,000 V according to selected voltage reference (Vref). Remember that the four analog inputs available on CN5 are provided of filter capacitors that ensure an higher stability of the acquired signals, but reduce at the same time the bandwith frequency. For further informations please refer to the paragraph "TYPE OF ANALOG INPUT SELECTION".

#### **RESET KEY**

P1 reset key of the **GPC<sup>®</sup> 323** board allows the user to reset the board and restarting it in a general clearing condition.

The main purpose of this key is to come out of infinite loop conditions, useful especially during debug and develop phases, or to ensure a particular initial status. Please see figure 8 for an easy localization of this contact.

# grifo<sup>®</sup>

# **TEST POINT**

The board is provided with a test point called TP1, that allows to read, through a galvanically isolated multimeter, the reference voltage which is calibrated in laboratory and whose value is Vref=2.4900 V. TP1 is made of two contacts:

pin 1 -> Vref pin 2 -> GND

To easily locate the test point contacts please refer to figure 8, while for further informations about Vref signal please refer to the paragraph "TRIMMER AND CALIBRATION".

# **DIP SWITCH**

**GPC® 323** board is provided with one 8 pins dip switch (DSW1), typically used for system configuration, five of its pins a software readable by the User (DIP 1÷4, 8), two pins are used for memory configuration selection (DIP 5, 6), one pin is not used (DIP 7). The most frequent applications are: working condition selection or on board firmware parameters setting. The combination present on dip switch is in complemented logic (0 -> dip On and 1 -> dip OFF) and can be read performing a read operation at the address decided by the on board control logic for the dip switch. For further informations please refer to the paragraphs "I/O MAPPING" and "MEMORY MAPPING", while to easily locate the dip switch please refer to figure 8.

# **POWER SUPPLY VOLTAGES**

**GPC<sup>®</sup> 323** board is provided with and efficent circuitry that solves in an efficent and comfortable way the problem of power supply in any employ condition. Here follows the list of the possible configurations for power supply section:

- No power supply section:

The board must be supplied by a +5 Vdc voltage provided directly on the specific pins of CN1, CN3A or CN3B.

- Linear power supply section:

The board must be supplied by a  $6 \div 12$  Vac altenate voltage, or the corresponding continuous voltage, that must be provided to pins 1 and 2 of CN4. This is the high efficence linear supply section.

It is also available a normal efficence linear supply section, which requires 8÷12 Vac, or the corresponding continuous voltage, as input supply.

- Switching power supply section:

The board must be supplied by a 15÷24 Vac alternate voltage, or the corresponding continuous voltage, that must be provided to pin 1 and 2 of CN4.

Regardless the type of supply section chosen, the **GPC**<sup>®</sup> **323** board is always provided with an efficent protection circuitry that protects the board against voltage peaks or noise. Please remark that the desired supply section must be explicitally specified in the order; in fact the choice implies a different hardware configuration that must be performed by the grifo® technical pesonnel.

# **INTERRUPTS MANAGEMENT**

One of the most important **GPC® 323** features is the powerful interrupts management. Here is a short description of how the board's hardware interrupt signals can be managed; a more complete description of the hardware interrupts can be found in the microprocessor data sheets or in appendixes of this manual.

| /INT <b>ABACO®</b> I/O BUS | -> generates an interrupt on CPU pin 14 (/INT0) |

|----------------------------|-------------------------------------------------|

| /NMI ABACO® I/O BUS        | -> generates an interrupt on CPU pin 2 (T2)     |

This connections allow to generate an interrupt when the /NMI CPU signals is actived, through an opportune programming of microprocessor inside timer 2 and is remarkable the possibility to use this feature with **ZBT xxx** and **ZBR xxx** board. In fact optocoupled input signals of these two boards cna generate interrupts or simply be counted.

There are also microprocessor inside resources that can generate interrupts.

## **TYPE OF ANALOG INPUT SELECTION**

**GPC® 323** board can accept analog voltage and/or current inputs, as described in the previous paragraphs and chapters. The input type selection can be made only for 8 out of 11 input analog channels during the order phase and is performed mounting a specific voltage-current conversion module made by precision resistors. In detail:

| R37 | -> | channel 0 |

|-----|----|-----------|

| R36 | -> | channel 1 |

| R35 | -> | channel 2 |

| R34 | -> | channel 3 |

| R33 | -> | channel 4 |

| R32 | -> | channel 5 |

| R31 | -> | channel 6 |

| R30 | -> | channel 7 |

Should the voltage-current conversion module not to be mounted (default case) the corresponding channel accepts a voltage input signal in the range 0÷2.49 V; otherwise a current input signal is accepted.

The value of the above mentioned resistors is obtained by the following spread;

#### R = 2.49 V / Imax

Usually the voltage-current conversion modules are made using 124  $\Omega$  precision resistors, corresponding to 4÷20 mA or 0÷20 mA.

To easily locate the voltage-current conversion module please refer to figure 8.

#### grifo<sup>®</sup> -

# TRIMMERS AND CALIBRATION

On GPC<sup>®</sup> 323 is available a trimmer, named RV1, that calibrates the Vref voltage of the A/D converter section. The GPC<sup>®</sup> 323 is subjected to a carefull test that verifies and calibrates all the card sections. To easily locate the trimmer, please refer to figure 8. The calibration is executed in laboratory, with a conntrolled +20 C<sup>°</sup> room temperature, following these steps:

- -The A/D voltage reference (Vref) is calibrated through RV1 trimmer, by using a 5 digits precision multimeter, to a value of +2,4900 Vdc or +5,0000 Vdc.

- The corrispondance between the analog input signal and the combination read from A/D is verified. This check is performed with a reference signal connected to A/D inputs and testing that the A/D combination and the theoric combination differ at maximum of the A/D section errors sum.

- The trimmer is blocked with paint.

The analog interfaces use high precision components that are selected during mounting phase to avoid complicate and long calibration procedures. After the calibration, the on board trimmer is blocked with paint to mantain calibration also in presence of mechanic stresses (vibrations, movings, delivery, etc.).

The user must not modify the card calibration, but if thermic drifts, time drifts and so on, make necessary a new calibration, the user must strictly follow the previous described procedure.

## JUMPERS

On **GPC<sup>®</sup> 323**there are 17 jumpers for card configuration, 8 of them are solder jumpers. Thanks to these jumpers, the user can define for example the memory type and size, the peripheral devices functionality and so on. Below there is the jumpers list, location and function.

| JUMPER   | N. PINS | USE                                                                                     |

|----------|---------|-----------------------------------------------------------------------------------------|

| J1       | 2       | Connects to + 5 Vcc CN1 pin 26.                                                         |

| J2       | 3       | Selects memory device type for IC 3.                                                    |

| J3       | 3       | Selects memory device type and size for IC 3.                                           |

| J4       | 3       | Selects memory device type and size for IC 3.                                           |

| J5       | 3       | Selects memory device size for IC 4.                                                    |

| J6       | 2       | Configures back up circuitry for RAM and RTC.                                           |

| J7       | 6       | Selects direction and activation modality for RS 422-485 serial line.                   |

| J8       | 2       | Connects watchdog external circuitry.                                                   |

| J18      | 3       | Selects the connection type for CPU pin 14 (/INT0).                                     |

| JS1, JS2 | 2       | Connect the termination and forcing circuitry for RS 422-485 serial communication line. |

| JS3      | 3       | Selects the connection type for CN3A pin 1.                                             |

| JS4      | 3       | Selects the connection type for CN3B pin 1.                                             |

| JS5      | 2       | Selects internal or external ROM code area.                                             |

| JS7,JS8  | 2       | Connect RS 232 driver of serial A to CN3A.                                              |

| JS9      | 3       | Selects the communication type for serial A reception line.                             |

#### FIGURE 23: JUMPERS SUMMARIZING TABLE

The following tables describe all the right connections of **GPC**<sup>®</sup> **323**jumpers with their relative functions. To recognize these valid connections, please refer to the board printed diagram (serigraph) or to figure 2 of this manual, where the pins numeration is listed; for recognizing jumpers location, please refer to figures 24 and 26. The "\*" used in the following tables, denotes the default connection, or on the other hand the connection set up at the end of testing phase, that is the configuration the user receives.

Ç

FIGURE 24: COMPONENT SIDE JUMPERS LOCATION

# 2 PINS JUMPERS

| JUMPER   | CONNECTION USE                                                                                                              |                                                                                                                                                                                   | DEF. |

|----------|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| J1       | not conncted                                                                                                                | Does not connect CN1 pin 26 to +5 Vcc.                                                                                                                                            |      |

|          | connected                                                                                                                   | Connects CN1 pin 26 to +5 Vcc.                                                                                                                                                    | *    |

| J6       | not conncted IC 4 RAM backed only by an eventual<br>external battery.<br>IC12 RAM +RTC backed only by on bo<br>battery BT1. |                                                                                                                                                                                   | *    |

|          | connected                                                                                                                   | IC 4 RAM backed by an eventual external<br>battery and the eventual on board battery<br>BT1.<br>IC12 RAM +RTC backed by on board battery<br>BT1 and an eventual external battery. |      |

| J8       | not conncted                                                                                                                | Does not connect external watchdog circuitry to reset circuitry.                                                                                                                  | *    |

|          | connected                                                                                                                   | Connects external watchdog circuitry to reset circuitry.                                                                                                                          |      |

| JS1, JS2 | not conncted                                                                                                                | Do not connect the termination and forcing circuitry RS 422-485 serial A.                                                                                                         | *    |

|          | connected                                                                                                                   | Connect the termination and forcing circuitry RS 422-485 serial A.                                                                                                                |      |

| JS5      | not conncted                                                                                                                | Enables microprocessor inside ROM code.                                                                                                                                           |      |

|          | connected                                                                                                                   | Enables external ROM = on board EPROM                                                                                                                                             | *    |

| JS7, JS8 | not conncted                                                                                                                | Do not connect RS 232 driver of serial A to CN3A.                                                                                                                                 |      |

|          | connected                                                                                                                   | Connect RS 232 driver of serial A to CN3A.                                                                                                                                        | *    |

# FIGURE 25: 2 PINS JUMPERS TABLE

The "\*" used in the following tables, denotes the default connection, or on the other hand the connection set up at the end of testing phase, that is the configuration the user receives.

FIGURE 26: SOLDER SIDE JUMPERS LOCATION

# **3 PINS JUMPERS**

| JUMPER | CONNECTION    | USE                                                                      | DEF. |

|--------|---------------|--------------------------------------------------------------------------|------|

| J2     | position 1-2  | Sets IC3 to accept EPROM.                                                |      |

|        | position 2-3  | Sets IC3 to accept RAM/EEPROM.                                           | *    |

| J3     | position 1-2  | Sets IC3 to accept EPROM                                                 |      |

|        | position 2-3  | Sets IC3 to accept 32K RAM/EEPROM.                                       | *    |

|        | not connected | Sets IC3 to accept 8K RAM/EEPROM.                                        |      |

| J4     | position 1-2  | Sets IC3 to accept 32K<br>RAM/EEPROM/EPROM.                              | *    |

|        | position 2-3  | Sets IC3 to accept 8K RAM/EEPROM.                                        |      |

|        | not connected | Sets IC3 to accept 8K EPROM.                                             |      |

| J5     | position 1-2  | Sets IC4 to accept 32K RAM/EEPROM.                                       | *    |

|        | position 2-3  | Sets IC4 to accept 8K RAM/EEPROM.                                        |      |

| J18    | position 1-2  | Connects CPU pin 14 (/INT0) to CN1 pin 23 (/INT).                        |      |

|        | position 2-3  | Connects CPU pin 14 (/INT0) to IC25 pin 12 (serial B reception signal).  | *    |

| JS3    | position 1-2  | Connects CN3A pin 1 to GND.                                              | *    |

|        | posizione 2-3 | Connects CN3A pin 1 to +5 Vdc.                                           |      |

| JS4    | position 1-2  | Connects CN3B pin 1 to GND.                                              | *    |

|        | position 2-3  | Connects CN3B pin 1 to +5 Vdc.                                           |      |

| JS9    | position 1-2  | Connects serial A reception signal to RS 232 driver.                     | *    |

|        | position 2-3  | Connects serial A reception signal to Current Loop or RS 422-485 driver. |      |

# FIGURE 27: 3 PINS JUMPERS TABLE

The "\*" used in the following tables, denotes the default connection, or on the other hand the connection set up at the end of testing phase, that is the configuration the user receives.

# 6 PINS JUMPERS

| JUMPER | CONNECTION           | USE                                                                          | DEF. |

|--------|----------------------|------------------------------------------------------------------------------|------|

| J7     | position 1-2 and 3-4 | Selects RS 485 serial communication (2 wires half duplex)                    |      |

|        | position 2-3 and 4-5 | Selects RS 422-485 serial communication (4 wires full duplex or half duplex) |      |

|        | position 1-6         | Connects the il RTC interrupt signal to CPU pin 15 (P3.3 - /INT1).           | *    |

# FIGURE 28: 6 PINS JUMPERS TABLE

The "\*" used in the following tables, denotes the default connection, or on the other hand the connection set up at the end of testing phase, that is the configuration the user receives.

# <u>NOTE</u>

Here follow some indications about how to configure properly the board.

# BACK UP

Please remark that lithium battery BT1 is optional and is provided only with IC12 RAM+RTC:

- If the User needs toback up IC14 RAM then he/she must connect an external battery to CN2. Through jumper J6 it is also possible to back up the optional IC12 RAM+RTC module, saving the on board battery BT1.

- If the board is provided with on board battery BT1, through jumper J6 the Use can also back up IC4 RAM, but only for short time periods, like, for example, to perfrom the replacement of the external battery.

No other combination has been considered therefore no other combination can be used. To choose the external battery please follow the indications at the paragraph "ELECTRIC FEATURES".

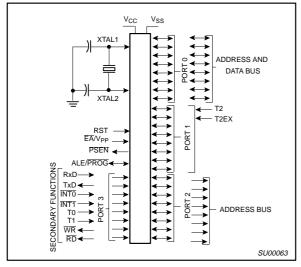

# SERIAL COMMUNICATION TYPE SELECTION

The serial line A is available on connector CN3A and can be buffered in RS 232, RS 422, RS 485 or Current Loop electric standard. By hardware can be selected which one of these electric standard is used, through jumpers connection. By software the serial line can be programmed to operate with the desired physical communication protocol acting on the CPU internal registers. In the following paragraphs there are all the informations on serial communication configurations; please note that jumers which are not metioned below do not affect the serial communication whatever their configuration is.

# - RS 232 SERIAL LINE

MAX 232 serial driver must be installed on IC25, while on IC26, IC27, IC28, IC29 no driver must be installed. Jumper JS9 must be connected in position 1-2, jumpers JS7 and JS8 must be connected.

- arifo®

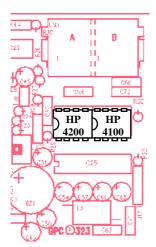

## - CURRENT LOOP SERIAL LINE

HCPL 4100 must be installed n IC26, HCPL 4200 must be installed on IC28, while on IC17 and IC29 no driver must be installed. Jumper JS9 must be connected in position 2-3, jumpers JS7 and JS8 must be not connected..

#### - RS 485 SERIAL LINE

SN75176 serial driver must be installed on IC27, while no driver must be installed on IC26 and IC28. Jumper J7 must be connected in position 1-2 and 3-4, jumper JS9 must be connected in position 2-3, jumpers JS7 and JS8 must be not connected. CN3A pins 4 and 5 are the singnals emploied to receive and transmit according to the status of DIR signal (0=level low=reception, 1=level high=transmission), which is software manageable

This kind of serial communication cab be used for multi-point connections, in addition it is possible to listen to own transmission, so the user is allowed to verify the succes of transmission. In fact, any conflict on the linecan be recognized by testing the received character after each transmission.

## - RS 422 SERIAL LINE

SN75176 serial drivers must be installed on IC27 and IC29 while no driver must be installed on IC26 and IC28. Jumper J7 must be connected in position 2-3 and 4-5, jumper JS9 must be connected in position 2-3, jumpers JS7 and JS8 must be not connected.

DIR signal can be kept always high (active transmittrer) for point-to-point connections, while for multi-point connections the transmitter must be actived only before the transmission (DIR =1=high=transmitter actived).

If using the RS 422-485 serial line, it is possible to connect the terminating and forcing circuit on the line by using JS1 and JS2. This circuit must be always connected in case of point-to-point connections, while in case of multi-point connections it must be connected olny in the farest boards, that is on the edges of the communication line.

To easily locate jumpers and serial drivers please refer to appendix A.

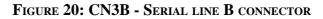

**GPC® 323** board is provided with a second serial line (B) that can be buffered only as RS 232. Serial line B is software managed through two microcontroller I/O signals, so communication parameters can be set programming the management firmware (for further informations please refer to the software tool manual). Please remark that RxB reveption signal can be connected to CPU /INTO signal connecting jumper J18 in position 2-3 allowing to manage the reception via interrupt.

C

ITALIAN TECHNOLOGY -

# grifo<sup>®</sup> -

# **MEMORY SELECTION**