# **CI/O R16**

# **Coupled Input Output NPN Relays**

# TECHNICAL MANUAL

Via dell' Artigiano, 8/6 40016 San Giorgio di Piano (Bologna) ITALY E-mail: grifo@grifo.it

http://www.grifo.it http://www.grifo.com

Tel. +39 051 892.052 (a. r.) FAX: +39 051 893.661

**CI/O R16**

Edition 5.00

Rel. 01 August 2000

GPC®, grifo®, are trade marks of grifo®

# **CI/O R16**

# **Coupled Input Output NPN Relays**

# TECHNICAL MANUAL

Single Europe format size 100x160 mm; **ABACO**® BUS industrial interface; 16 digital output signals with 1A 24V relays;MOV 24Vac transient suppressors on each relay; 16 LEDs to visualize the relays status; debouncing circuitry on each relays; 16 digital optocoupled NPN input signals with π filter on each input; 16 LEDs to visualize the logic status of each optocouped input; I/O mapping selection through on board Dip Switch; addressing space needed as low as 2 bytes contiguous; possibility to connect or disconnect the BUS /RESET signal; 20 pins standard input connector and 34 pins standard output connector; possibility to have two different versions of power supply: **CI/O R16** (multi supply version: 5Vdc and 12Vdc for relays) and **CI/O R16.05** (single supply version: 5Vdc).

Via dell' Artigiano, 8/6 40016 San Giorgio di Piano (Bologna) ITALY

E-mail: grifo@grifo.it

http://www.grifo.it http://www.grifo.com Tel. +39 051 892.052 (a. r.) FAX: +39 051 893.661

**CI/O R16**

Edition 5.00

Rel. 01 August 2000

GPC®, grifo®, are trade marks of grifo®

# DOCUMENTATION COPYRIGHT BY grifo®, ALL RIGHTS RESERVED

No part of this document may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means, either electronic, mechanical, magnetic, optical, chemical, manual, or otherwise, without the prior written consent of **grifo**<sup>®</sup>.

# **IMPORTANT**

Although all the information contained herein have been carefully verified, **grifo**<sup>®</sup> assumes no responsability for errors that might appear in this document, or for damage to things or persons resulting from technical errors, omission and improper use of this manual and of the related software and hardware.

**grifo**® reserves the right to change the contents and form of this document, as well as the features and specification of its products at any time, without prior notice, to obtain always the best product.

For specific informations on the components mounted on the card, please refer to the Data Book of the builder or second sources.

# **SYMBOLS DESCRIPTION**

In the manual could appear the following symbols:

Attention: Generic danger

Attention: High voltage

#### **Trade Marks**

, GPC<sup>®</sup>, grifo<sup>®</sup>: are trade marks of grifo<sup>®</sup>.

Other Product and Company names listed, are trade marks of their respective companies.

# **GENERAL INDEX**

| INTRODUCTION                            | 1   |

|-----------------------------------------|-----|

| CARD VERSION                            | 1   |

| GENERAL INFORMATIONS                    | 2   |

| INTERFACING AND ADDRESSING SECTION      | 4   |

| CONTROL LOGIC                           | 4   |

| OUTPUT SECTION                          | 4   |

| INPUT SECTION                           | 4   |

| TECHNICAL FEATURES                      | 6   |

| GENERAL FEATURES                        | 6   |

| ELECTRIC FEATURES                       | 6   |

| PHYSICAL FEATURES                       | 7   |

| INSTALLATION                            | 8   |

| CONNECTIONS                             | 8   |

| CN1 - CONNECTOR FOR OPTOCOUPLED INPUTS  | 8   |

| CN2 - CONNECTOR FOR RELAY OUTPUTS       |     |

| K1 - CONNECTOR FOR ABACO® BUS           |     |

| VISUAL SIGNALATIONS                     |     |

| RESET CIRCUITRY CONFIGURATION           |     |

| JUMPERS                                 |     |

| I/O CONNNECTIONS                        |     |

| POWER SUPPLY                            |     |

| HARDWARE DESCRIPTION                    | 19  |

| BOARD MAPPING                           |     |

| INTERNAL REGISTERS ADDRESSING           | 20  |

| PERIPHERAL DEVICES SOFTWARE DESCRIPTION | 21  |

| RELAY OUTPUTS                           | 21  |

| OPTOCOUPLED INPUTS                      |     |

| EXTERNAL CARDS                          | 23  |

| BIBLIOGRAPHY                            | 28  |

| APPENDIX A: ALPHABETICAL INDEX          | A-1 |

Rel. 5.00

# FIGURE INDEX

| FIGURE 1: BLOCK DIAGRAM                                     | 3  |

|-------------------------------------------------------------|----|

| FIGURE 2: COMPONENTS MAP                                    |    |

| FIGURE 3: CN1 - CONNECTOR FOR OPTOCOUPLED INPUTS            |    |

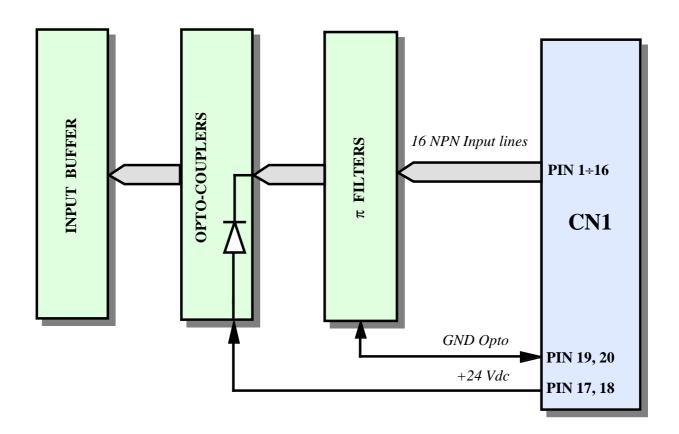

| FIGURE 4: OPTOCOUPLED INPUTS BLOCK DIAGRAM                  | 9  |

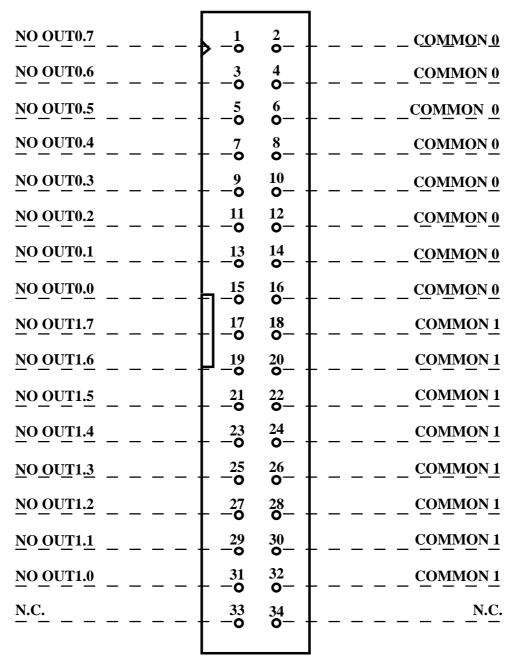

| FIGURE 5: CN2 - RELAYS OUTPUTS CONNECTOR                    | 10 |

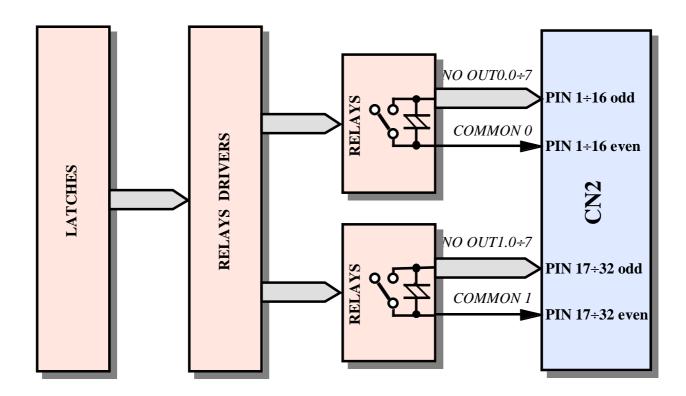

| FIGURE 6: RELAYS OUTPUTS BLOCK DIAGRAM                      | 11 |

| FIGURE 7: K1 - CONNECTOR FOR ABACO® BUS                     | 12 |

| FIGURE 8: VISUAL SIGNALATIONS TABLE                         | 14 |

| FIGURE 9: CONNECTORS, DIP SWITCH, LEDS AND JUMPERS LOCATION | 15 |

| FIGURE 10: JUMPERS TABLE                                    | 16 |

| FIGURE 11: CARD PHOTO                                       | 17 |

| FIGURE 12: INTERNAL REGISTERS ADDRESING TABLE               | 20 |

| FIGURE 13: POSSIBLE CONNECTIONS DIAGRAM                     | 25 |

#### INTIRODUCTION

The use of these devices has turned - IN EXCLUSIVE WAY - to specialized personnel.

The purpose of this handbook is to give the necessary information to the cognizant and sure use of the products. They are the result of a continual and systematic elaboration of data and technical tests saved and validated from the manufacturer, related to the inside modes of certainty and quality of the information.

The reported data are destined- IN EXCLUSIVE WAY- to specialized users, that can interact with the devices in safety conditions for the persons, for the machine and for the environment, impersonating an elementary diagnostic of breakdowns and of malfunction conditions by performing simple functional verify operations , in the height respect of the actual safety and health norms.

The informations for the installation, the assemblage, the dismantlement, the handling, the adjustment, the reparation and the contingent accessories, devices etc. installation are destined - and then executable - always and in exclusive way from specialized warned and educated personnel, or directly from the TECHNICAL AUTHORIZED ASSISTANCE, in the height respect of the manufacturer recommendations and the actual safety and health norms.

The devices can't be used outside a box. The user must always insert the cards in a container that rispect the actual safety normative. The protection of this container is not threshold to the only atmospheric agents, but specially to mechanic, electric, magnetic, etc. ones.

To be on good terms with the products, is necessary guarantee legibility and conservation of the manual, also for future references. In case of deterioration or more easily for technical updates, consult the AUTHORIZED TECHNICAL ASSISTANCE directly.

To prevent problems during card utilization, it is a good practice to read carefully all the informations of this manual. After this reading, the user can use the general index and the alphabetical index, respectly at the beginning and at the end of the manual, to find information in a faster and more easy way.

# CARD VERSION

The present manual is reported to the CI/O R16 version 280795.

The validity of the bring informations is subordinate to the number of the card release. The user must always verify the correct correspondence among the two denotations. Version number is printed on the boards in several positions both in serigraph and in printed circuit (for example nrear DSW1 on the component side).

#### GENERAL INFORMATIONS

La CI/O R16 (Coupled Input Output 16 Relays and 16 NPN inputs) is a powerfull digital I/O module that provides on one only board the features normally available on two boards. This extreme compactness, distinctive feature of grifo® boards, allows to optimize room and cost of the final application. The board uses only as low as two bytes of addressing space, distinguishing the two locations for read or write operations. No software initialization is needed to use the board. When a Power on or Reset occour CI/O R16 disables the 16 relays through a specific circuitry (if it has no been excluded by moving a jumper) warranting so the absence of any kind of bounce on the output contacts. Only after a write operation to one of its two registers the protection circuitry allows the activation of the relays and awarns that the board is working properly by lighting the LED corresponding to the register. All the output relays are provided with a MOV transient suppressor and a LED to indicate is the relay is actived or not.

The sixteen input signals, galvanically isolated and NPN type, are provided with a  $\pi$  filter and a LED to indicate the status of each single input. This solution allows an high immunity to the disturbs and the possibility to see immediatly the situation of the inputs.

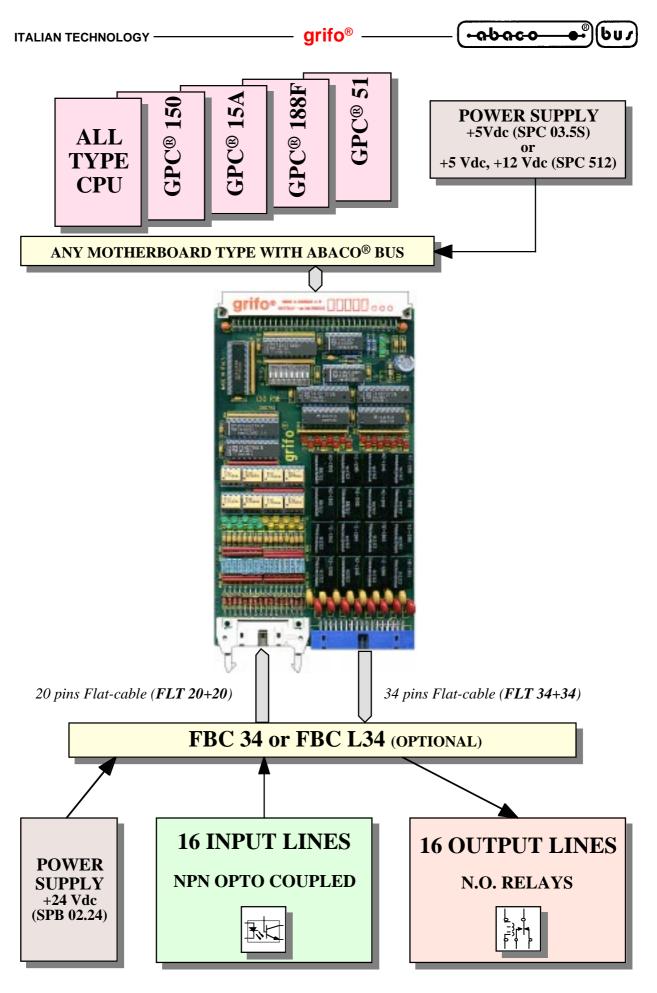

The connection with the external world is performed through two comfortable standard I/O connectors located on the front of the board. One of the connectors is dedicated to inputs, the other one is dedicated to outputs. This separation increases the safety in the working of the board.

To simplify the connection of the several signals to the external world, the BLOCK modules of FBC seria are available. These modules have been designed to unravel the signals coming from the two flat cables to comfortable quick release screw terminal connectors. The best choices are **FBC 34**, **FBC 20**, **FBC 120**, **FBC L34** e **FBC L20**. The latter two **FBC**, **L34** and **L20**, allow to visualize the signals status through LEDs, making easier the task to control the correct cables connections even when the board is already in a Rack.

Aremarkable feature of **CI/O R16** is the availability of a single power supply version (5 Vdc) in addition to the version with two power supplies (5 Vdc for logic circuits and 12 Vdc for the relays). This feature is intresting especially to reduce costs and room occupied in small applications.

- Single Europe format size 100x160 mm

- ABACO® BUS industrial interface

- **16** digital output signals with 1A 24V relays

- MOV 24Vac transient suppressors on each relay

- 16 LEDs to visualize the relays status

- Debouncing circuitry on each relays

- 16 digital optocoupled NPN input signals with  $\pi$  filter on each input

- 16 LEDs to visualize the logic status of each optocouped input

- I/O mapping selection through on board Dip Switch

- Addressing space needed as low as 2 bytes contiguous

- Possibility to connect or disconnect the BUS /RESET signal

- 20 pins standard input connector and 34 pins standard output connector

- Possibility to have **two** different **versions** of power supply:

CI/O R16 Multi supply version: 5 Vdc 90 mA and 12 Vdc 300 mA for relays CI/O R16.05 Single supply version: 5 Vdc 700 mA.

Page 2 — CI/O R16 Rel. 5.00

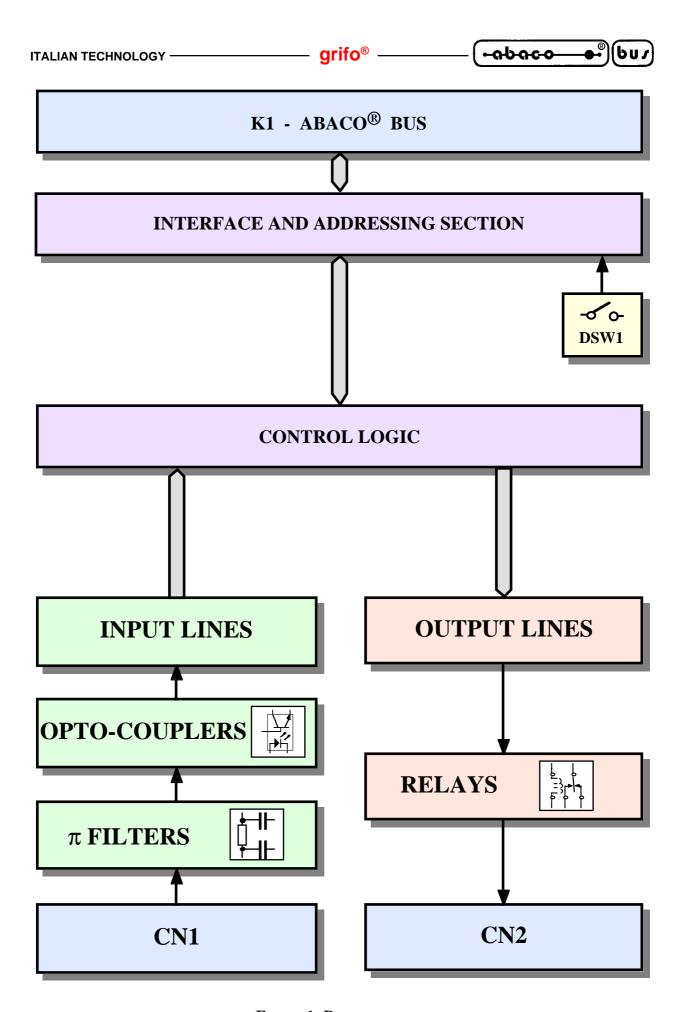

FIGURE 1: BLOCK DIAGRAM

Here follows a description of **CI/O R16** board's functional blocks, with an indication of the operations performed by each one. To easily locate these blocks and verify their connections pleare refer to figure 1.

#### INTERFACING AND ADDRESSING SECTION

This section manages the data exchange between contol logic and command board through ABACO® BUS. In particular, all written or read data transit across this section that, in addition, provides the board I/O management, by setting the dip switch **DSW1**.

For further informations please refer to the chapter dedicated to board's software description.

#### **CONTROL LOGIC**

This section generates all the chip select signals needed to acces the several peripherals on **CI/O R16** boards. Using this section the programmer can interact to the board's several sections, verifing their status, reading digital input configurations, setting output signals, etc.

All this can be done through a simple software management based on **ABACO® BUS**, to which the contol logic connects through the interfacing and addressing section. For further informations please refer to the chapter dedicated to board's software description.

#### **OUTPUT SECTION**

This section features 16 Output signals driven by one or more latches. These components are managed through specific read/write registers, according to the informations contained in the chapters dedicated to board's hardware and software description. Any Output signal, visualized through its own LED, controls a 1A Relay, normally open, provided with a MOV 24 Vac noise suppressor. The power supply for the relays can be +12 Vdc, coming from **ABACO®** BUS (standard version of CI/O R16), or the same voltage of +5 Vdc that supplies the on board logic circuits (version CI/O R16.05). This latter solution allows to have an unique stabilized voltage to supply the whole system, with a greater total current consumption.

# **INPUT SECTION**

This section features 16 Input signals, acquired through input buffers. These components are managed by specific read/write registers, according to the informations contained in the chapters dedicated to board's hardware and software description. Any Input signal is galvanivally isolated, NPN type and visualized through its own LED. Optocouplers of this section are supplied through +24 Vdc voltage that must be provided by means of a specific connector. All the input signals are protected by a  $\pi$  filter, that warrants a high immunity against the disturbs from the external world.

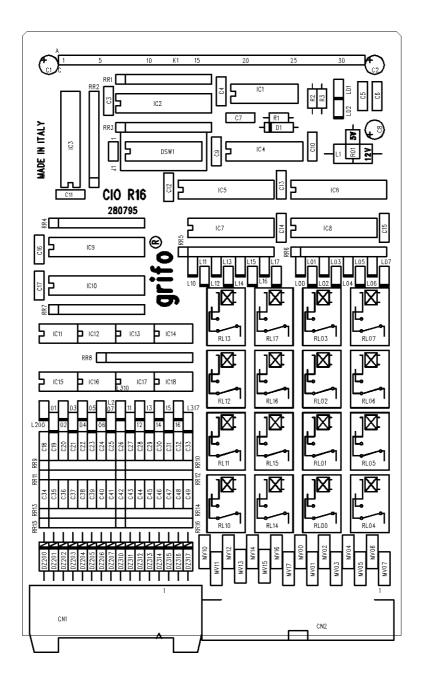

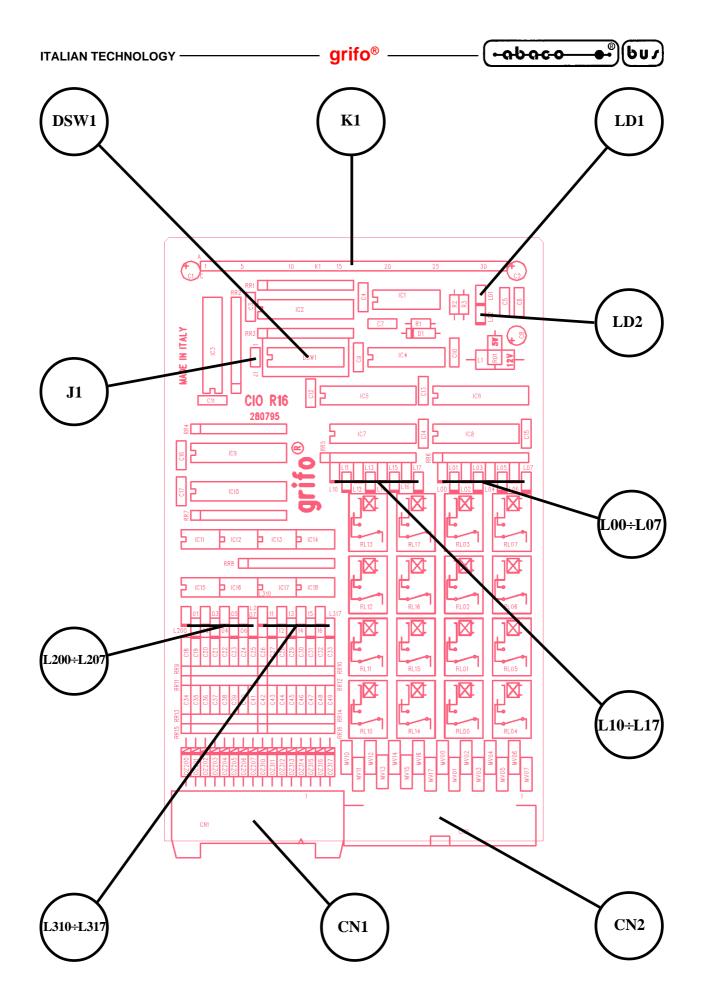

FIGURE 2: COMPONENTS MAP

# TECHNICAL FEATURES

# **GENERAL FEATURES**

On board resources: 16 Input optocoupled NPN

16 Output 1A relays N.O.

8 pins Dip switch to set the I/O addressing

BUS type: ABACO® Industrial

8 bits data and addresses

N. addressable bytes: 256

N. bytes occupied: 2

#### **ELECTRIC FEATURES**

Standard version CI/O R16

**Power supply:** +5 Vdc (logic circuits)

+12 Vdc (relays)

+ 24 Vdc (optoicoupled inputs)

**Current consumption:** 90 mA (+5 Vdc)

300 mA (+12 Vdc)

140 mA (+24 Vdc)

Single supply version CI/O R16.05

**Power supply:** +5 Vdc (logic circuits and relays)

+ 24 Vdc (optoicoupled inputs)

**Current consumption:** 700 mA (+5 Vdc)

140 mA (+24 Vdc)

Max current on the relay contact: 1 A

**Max voltage on the relay contact:** 24 Vac / 24 Vdc

Should the User need to connect higher voltages

please contact grifo®

**Relays protection:** 24 Vac MOV transient suppresor

**Filter on NPN inputs:**  $\pi$  filter

| TALIAN TECHNOLOGY | ——— grifo® ——— | — (-abaco—•®(bu/ |

|-------------------|----------------|------------------|

|-------------------|----------------|------------------|

# **PHYSICAL FEATURES**

Size: Standard EUROPE format 100x160 mm

**Weight:** 210 g

Connectors: K1: DIN 41612 64 pins M 90° A+C type C

CN1: Low profile 20 pins M 90°

strain relief clamp

CN2: Low profile 34 pins M 90°

**Temperature range:** from 0 to 70 centigrad degreeses

**Relative humidity:** 20% up to 90% (without condense)

#### INSTALLATION

In this chapter there are the information for a right installation and correct use of **CI/O R16** card. The User can find the location and functions of each connectors, jumpers and some explanatory diagrams.

#### **CONNECTIONS**

The **CI/O R16** card has several connectors that can be linkeded to other devices or directly to the field, according to system requirements. In this paragraph there are connectors pin outs, a short signals description (including the signals direction) and connectors location (please see figure 9), plus some figures that describe how the interface signals are connected on the card.

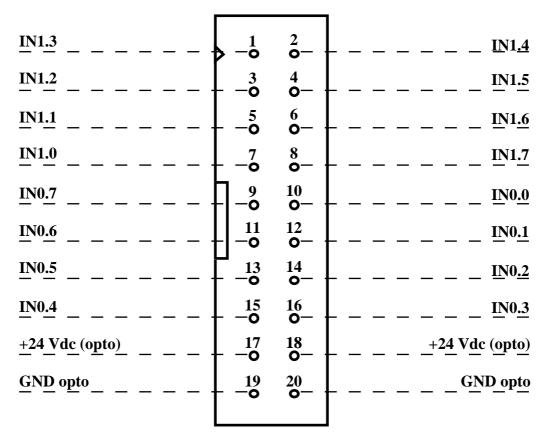

#### CN1 - CONNECTOR FOR OPTOCOUPLED INPUTS

The connector for optocoupled NPN inputs, called CN1, is a low profile, 2.54 mm pitch, 90 degreeses, 20 pins connector.

The connector features the 16 inputs of **CI/O R16** and the lines to supply the optocouplers.

FIGURE 3: CN1 - CONNECTOR FOR OPTOCOUPLED INPUTS

Page 8 — CI/O R16 Rel. 5.00

Signals description:

IN0.n = I - n-th optocoupled NPN input n of section IN0. IN1.n = I - n-th optocoupled NPN input n of section IN1.

+24 Vdc (opto) = I - Optocouplers power supply for sections IN0 and IN1.

**GND opto** = - Common terminal of optocouplers power supply for sections IN0 and IN1.

The NPN input signals available on **CI/O R16** are optocoupled and provided with  $\pi$  filter to warrant a high degree of protection against noise and disturbs from the external world. Each signal is provided with a LED for visual feed back (the LED will light whenever the input will have the potential of GND opto signal); this means that the inputs are going to support normally open contacts. These contacts are suitable to be connected to NPN drivers. In case the User would want to connect PNP drivers then he/she will have to put a **PBI 01** BLOCK module between the drivers and the card.

The interface circuitry for the 16 lines of the input section is shown in the following diagram. The supply voltage of the optocouplers must be +24 Vdc and must be provided through the specific pins of CN1.

.

FIGURE 4: OPTOCOUPLED INPUTS BLOCK DIAGRAM

#### **CN2 - CONNECTOR FOR RELAYS OUTPUTS**

The connectore for relays outputs, called CN2, is a low profile, 2.54 mm pitch, 90 degreeses, 34 pins connector. Normally open contacts of each relay output and two common terminals related to two output groups OUT0 and OUT1 are present; please remark that the maximum current for each relay is 1 A.

FIGURE 5: CN2 - RELAYS OUTPUTS CONNECTOR

# Signals descritpion:

**NO OUT0.n** = O - Contact of n-th normally open output in section OUT0.

**COMMON 0** = - Common contact of the 8 relays of secton OUTO.

**NO OUT1.n** = O - Contact of n-th normally open output in section OUT1.

**COMMON 1** = - Common contact of the 8 relays of secton OUT1.

**N.C.** = - Nt conneced.

Page 10 — CI/O R16 Rel. 5.00

The relays output signals available on **CI/O R16** are provided with a LED for visual feed back (the LED will light whenever the relay contact is closed); the relays are normally open, they can bear a maximum current of **1 A** with a maximum tension of **24 Vdc** or **24 Vac**.

The interface circuitry for this relays output section is shown in the following diagram.

#### **NOTE**

Should the User connect to the relays a voltage higher to the one declared in this manual, please contact **grifo**<sup>®</sup> directly; in fact this implies a different hardware configuration that must be performed by **grifo**<sup>®</sup> technicians.

The connector features the normally open contacts of each output and two common terminals related to output groups OUT0 and OUT1; when making the connections please remark that the maximun current for each relay is 1 A.

FIGURE 6: RELAYS OUTPUTS BLOCK DIAGRAM

CI/O R16 Rel. 5.00 ] — Page 11

# **K1 - CONNECTOR FOR ABACO® BUS**

The connector for **ABACO**® **industrial BUS**, called K1 on the board,is a DIN 41612, male, a 90 degeeses, type C, A+C.

Here follows the pin-out of the connector installed on **CI/O R16**, in addition there is the standard 8 bits and 16 bits**ABACO**® BUS pin-out.

Please remark that all the signals here described are TTL, except for the power supplies.

| A           | A          | A        | DIN | С        | C          | С           |

|-------------|------------|----------|-----|----------|------------|-------------|

| 16 bits BUS | 8 bits BUS | CI/O R16 | PIN | CI/O R16 | 8 bits BUS | 16 bits BUS |

| GND         | GND        | GND      | 1   | GND      | GND        | GND         |

| +5 Vdc      | +5 Vdc     | +5 Vdc   | 2   | +5 Vdc   | +5 Vdc     | +5 Vdc      |

| D0          | D0         | D0       | 3   | N.C.     |            | D8          |

| D1          | D1         | D1       | 4   | N.C.     |            | D9          |

| D2          | D2         | D2       | 5   | N.C.     |            | D10         |

| D3          | D3         | D3       | 6   | N.C.     | /INT       | /INT        |

| D4          | D4         | D4       | 7   | N.C.     | /NMI       | /NMI        |

| D5          | D5         | D5       | 8   | N.C.     | /HALT      | D11         |

| D6          | D6         | D6       | 9   | N.C.     | /MREQ      | /MREQ       |

| D7          | D7         | D7       | 10  | /IORQ    | /IORQ      | /IORQ       |

| A0          | A0         | A0       | 11  | /RD      | /RD        | /RDLDS      |

| A1          | A1         | A1       | 12  | /WR      | /WR        | /WRLDS      |

| A2          | A2         | A2       | 13  | N.C.     | /BUSAK     | D12         |

| A3          | A3         | A3       | 14  | N.C.     | /WAIT      | /WAIT       |

| A4          | A4         | A4       | 15  | N.C.     | /BUSRQ     | D13         |

| A5          | A5         | A5       | 16  | /RESET   | /RESET     | /RESET      |

| A6          | A6         | A6       | 17  | /M1      | /M1        | /IACK       |

| A7          | A7         | A7       | 18  | N.C.     | /RFSH      | D14         |

| A8          | A8         | N.C.     | 19  | N.C.     | /MEMDIS    | /MEMDIS     |

| A9          | A9         | N.C.     | 20  | N.C.     | VDUSEL     | A22         |

| A10         | A10        | N.C.     | 21  | N.C.     | /IEI       | D15         |

| A11         | A11        | N.C.     | 22  | N.C.     |            |             |

| A12         | A12        | N.C.     | 23  | N.C.     | CLK        | CLK         |

| A13         | A13        | N.C.     | 24  | N.C.     |            | /RDUDS      |

| A14         | A14        | N.C.     | 25  | N.C.     |            | /WRUDS      |

| A15         | A15        | N.C.     | 26  | N.C.     |            | A21         |

| A16         |            | N.C.     | 27  | N.C.     |            | A20         |

| A17         |            | N.C.     | 28  | N.C.     |            | A19         |

| A18         |            | N.C.     | 29  | N.C.     | /R.T.      | /R.T.       |

| +12 Vdc     | +12 Vdc    | +12 Vdc  | 30  | N.C.     | -12 Vdc    | -12 Vdc     |

| +5 Vdc      | +5 Vdc     | +5 Vdc   | 31  | +5 Vdc   | +5 Vdc     | +5 Vdc      |

| GND         | GND        | GND      | 32  | GND      | GND        | GND         |

FIGURE 7: K1 - CONNECTOR FOR ABACO® BUS

# Signals description:

#### 8 bits CPU

**A0-A15** = O - Address BUS **D0-D7** = I/O - Data BUS

**INT** = I - Interrupt request

**NMI** = I - Non Maskable Interrupt

$\mathbf{HALT} = \mathbf{O} - \mathbf{Halt}$  state

- Memory Request **MREQ** O = **IORQ** - Input Output Request 0 =RD O - Read cycle status - Write cycle status WR O - BUS Acknowledge **BUSAK** O

WAIT = I - Wait

BUSRQ = I - BUS Request

RESET = O - Reset

M1 = O - Machine cycle one

**RFSH** = O - Refresh for dynamic RAM

**MEMDIS** = I - Memory Display **VDUSEL** = O - VDU Selection

**IEI** = I - Interrupt Enable Input

CLK = O - System clock R.B. = I - Reset button

+5 Vdc = I - Power supply at +5 Vdc +12 Vdc = I - Power supply at +12 Vdc -12 Vdc = I - Power supply at -12 Vdc

**GND** = - Ground signal

#### 16 bits CPU

**A16-A22** = O - Address BUS **D8-D15** = I/O - Data BUS

- Read Upper Data Strobe RD UDS =O WR UDS =O - Write Upper Data Strobe **IACK** O - Interrupt Acknowledge = - Read Lower Data Strobe RD LDS =0 WR LDS =- Write Lower Data Strobe O

#### N.B.

Directionality indications as above stated are referred to a master (**CPU** o **GPC**<sup>®</sup>) board and have been kept untouched to avoid ambiguity in case of multi-boards systems.

# **VISUAL SIGNALATIONS**

**CI/O R16** card is provided with signalation LEDs to show several status informations, as described in the following table:

| LED       | COLOUR | PURPOSE                                                                                                                                            |

|-----------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| LD1       | Green  | When on, indicates that at least one write operation has been performed to section OUT1, after last Reset or Power-On happened.                    |

| LD2       | Green  | When on, indicates that at least one write operation has been performed to section OUTO, after last Reset or Power-On happened.                    |

| L00÷L07   | Red    | Visualize the status of the eight outputs of section OUT0, respectively OUT0.0÷OUT0.7. A LED on indicates an active output (relay contact closed). |

| L10÷L17   | Red    | Visualize the status of the eight outputs of section OUT1, respectively OUT1.0÷OUT1.7. A LED on indicates an active output (relay contact closed). |

| L200÷L207 | Green  | Visualize the status of the eight otocoupled input signals IN0, respectively IN0.0÷IN0.7. A LED on indicates an input contact closed.              |

| L310÷L317 | Yellow | Visualize the status of the eight otocoupled input signals IN0, respectively IN1.0÷IN1.7. A LED on indicates an input contact closed.              |

FIGURE 8: VISUAL SIGNALATIONS TABLE

The main purpose of LEDs is to show a visual indication about the card's status, making so easier debug and verify operations.

To easily locate these visual signalations please refer to the figure 9.

# **RESET CIRCUITRY CONFIGURATION**

Through dip switch **DSW1.1**, as described in the next paragraph, the User may select whether to connect or not the /RESET signal coming from **ABACO® BUS** to the specific circuitry on the board **CI/O R16**; if the dip is **ON**, when the /RESET is active the board's outputs are disabled. Viceversa if **DSW1.1** is **OFF**, /RESET signal doesn't affect the status of the outputs, that are disabled whenever a Power-On occours. This feature is essential when, for example, the outputs must not change status for a control board's reset due to, for example, an intervent of its on board Watch Dog circuitry.

Page 14 — CI/O R16 Rel. 5.00

FIGURE 9: CONNECTORS, DIP SWITCH, LEDS AND JUMPERS LOCATION

#### **JUMPERS**

On **CI/O R16** board there are 2 jumpers for card configuration. Below there is the jumpers list, location and function.

The following tables describe all the right connections of the three jumpers with their relative functions. For recognizing jumpers location, please refer to the figure 9.

The "\*" used in the following tables, denotes the default connection, or on the other hand the connection set up at the end of testing phase, that is the configuration the user receives.

| JUMPER       | CONNECTION | PURPOSE                                                                                                                  | DEF. |

|--------------|------------|--------------------------------------------------------------------------------------------------------------------------|------|

| J1 connected |            | Parallel interface does not manage signal /M1 coming from <b>ABACO</b> ® BUS.                                            |      |

|              |            | Parallel interface manages signal /M1 coming from ABACO® BUS.                                                            |      |

| DSW1.1       | OFF        | It does not connect the signal /RESET, coming from <b>ABACO</b> ® BUS, to the specific circuitry installed on the board. |      |

| DSW1.1       | ON         | It connects the signal /RESET, coming from <b>ABACO</b> ® BUS, to the specific circuitry installed on the board.         | *    |

FIGURE 10: JUMPERS TABLE

#### I/O CONNNECTIONS

To prevent possible connecting problems between **CI/O R16** board and the external systems, the User has to read carefully the information of the previous paragraphs and he must follow these instrunctions:

- To connect to the optocoupled input signals, only the contacts to acquire must be connected from the external system(s). These contacts (relays, switches, etc.) must connect or not connect the input signal INx.y to GND opto. About the correspondance between logic signals and contact status, an open contact generates a logic 1, a closed contact generates a logic 0, following the NPN standard.

- The relays output signals must be connected directly to the load to drive (power relays, etc.). The board provides the normally open contacts called NO OUTx.y, capable to bear a maximum current of 1 A with a tension that can be 24 Vdc or 24 Vac.

- To allow the User to drive several loads having different power supplies, each output section is provided with two differnt COMMON terminals connected to two groups of eight relays.

**NOTE:** Should the User connect to the relays a voltage higher to the one declared in this manual, please contact **grifo**<sup>®</sup> directly; in fact this implies a different hardware configuration that must be performed by **grifo**<sup>®</sup> technicians.

- The TTL output signals can be connected directly only to a device featuring the same type of interface. About the correspondance between logic signals and TTL output status, remember that a logic **0** generates a TTL 0 Vdc, while a logic **1** generates a TTL +5 Vdc.

Page 16 — CI/O R16 Rel. 5.00

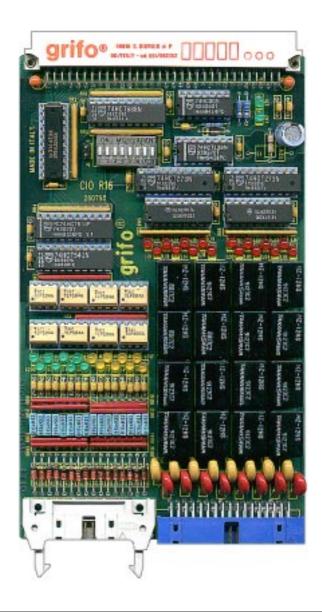

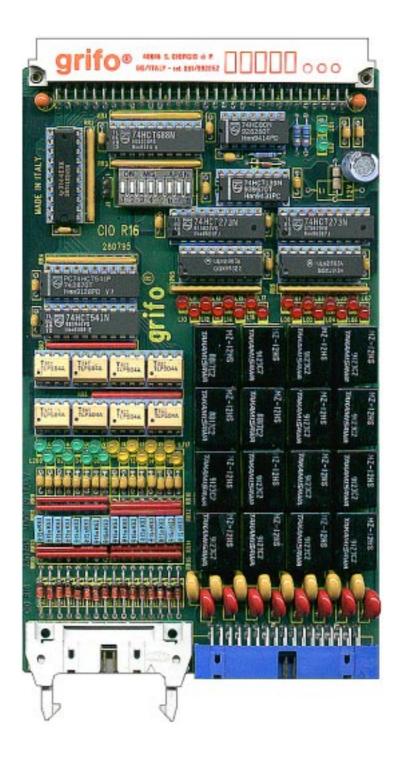

FIGURE 11: CARD PHOTO

#### **POWER SUPPLY**

CI/O R16 is provided with an efficient power supply circuitry that solves in an efficient and comfortable way the problem of board supply in any working condition. Here follow the needed voltages, according to the board version:

#### Standard version CI/O R16

+24 Vdc: Supplies the optocouplers in the input section of the board; must be about +24 Vdc and must be provided through pins 17-18 and 19-20 of CN1.

+5 Vdc: Supplies the control logic of the board; must be +5 Vdc  $\pm$  5% and must be provided through the specific pins of connector K1 (**ABACO**® BUS).

+12 Vdc: Supplies the relays of the board; must be  $+5 \text{ Vdc} \pm 5\%$  and must be provided through the specific pins of connector K1 (ABACO® BUS).

# Single supply version CI/O R16.05

+24 Vdc: Supplies the optocouplers in the input section of the board; must be about +24 Vdc and must be provided through pins 17-18 and 19-20 of CN1.

+5 Vdc: Supplies the control logic and the relays of the board; must be +5 Vdc  $\pm$  5% and must be provided through the specific pins of connector K1 (ABACO® BUS).

To warrant maximum noise immunity and so a correct working of the board, the +24 Vdc tension must be galvanically isolated from other tensions.

Please remark that the single supply version **CI/O R16.05** allows to use a single stabilized tension to supply the whole system, however in this case the current consumption is greater.

# HARDWARE DESCRIPTION

This chapter provides all the hardware informations needed to use **CI/O R16** board. Here the User will find informations about I/O card mapping and on board peripheral devices addressing.

#### **BOARD MAPPING**

**CI/O R16** board is mapped into a **2** bytes I/O addressing space, that can be mapped starting from different base addresses according to how the board is configured. This feature allows to use several **CI/O R16** cards on the same **ABACO**® BUS, or to install them on a BUS where other peripheral modules are installed obtaining a structure that can be expanded without any difficulty or modifications to the application software.

The base address can be defined through the specific BUS interface circuitry on the board itself; this circuitry uses the 8 pins dip switch called **DSW1**, from which it reads the address set by the User. Here follows the corrispondance between dips configuration and address signals.

DSW1.1 Please see paragraph JUMPERS **DSW1.2** Address A1 -> Address A2 DSW1.3 -> DSW1.4 Address A3 -> **DSW1.5** -> Address A4 DSW1.6 Address A5 -> DSW1.7 Address A6 -> **DSW1.8** Address A7 ->

These dips are driven in complemented logic, this means that if a jumper is **CONNECTED** generates a **logic zero**, viceversa if a jumper is **NOT CONNECTED** generates a **logic one**.

Also jumper J1, described in the previous paragraph, affectes the addressing logic and must be connected according to the type of control card (**GPC**<sup>®</sup> serie) is used. In detail if the control card is provided with signal /M1 on the **ABACO**<sup>®</sup> BUS connector, then jumper J1 must be connected and vicecersa.

When allocating the mapping address of the boards, plase be careful not to allocate more than one device in the same addressing space (count also the number of bytes occupied by the card). If this condtion will not be respected, a BUS conflict will happen; such conflict will compromise the correct working of the whole system.

CI/O R16 Rel. 5.00 Page 19

As an example, a possible mapping is reported here.

If the User should map **CI/O R16** board, controlled by a card provided with /M1 signal, from address 04AH, jumpers and dips should be configured like this:

| J1     | -> | Connected |

|--------|----|-----------|

| DSW1.2 | -> | OFF       |

| DSW1.3 | -> | ON        |

| DSW1.4 | -> | OFF       |

| DSW1.5 | -> | ON        |

| DSW1.6 | -> | ON        |

| DSW1.7 | -> | OFF       |

| DSW1.8 | -> | ON        |

To easily locate these components please refer to figures 2 and 9.

# **INTERNAL REGISTERS ADDRESSING**

Indicating the board base address with **<base>baseaddr>**, that is the address set using Dip Switch DSW1, as indicated in the previous paragraph **CI/O R16** internal registers are addressable as explained in the following tables.

#### **NOTE**

If using several boards on the same **ABACO® BUS**, when setting the boards mapping address the User shold be careful not to allocate more than one board in the same addressing space (consider the base address plus the bytes taken by the board addressing). If this condition is not satisfied a BUS conflict situation will occour, prejudicing the correct working of the whole system.

| DEVICE   | REG. | ADDRESS          | R/W | PURPOSE                                                                 |

|----------|------|------------------|-----|-------------------------------------------------------------------------|

| OUTPUT 0 | OUT0 | <base/> ddr>+00H | W   | Registro to set the status of the 8 relay outputs in section OUT0.      |

| OUTPUT 1 | OUT1 | <base/> ddr>+01H | W   | Registro to set the status of the 8 relay outputs in section OUT1.      |

| INPUT 0  | IN0  | <base/> ddr>+00H | R   | Registro to read the status of the 8 optocpupled inputs in section IN0. |

| INPUT 1  | IN1  | <base/> ddr>+01H | R   | Registro to read the status of the 8 optocpupled inputs in section IN1. |

FIGURE 12: INTERNAL REGISTERS ADDRESING TABLE

#### PERIPHERAL DEVICES SOFTWARE DESCRIPTION

In the previous paragraph allocation addresses of all the peripherals have been reported, here follows a detailed description of function and meaning of internal registers (please always refer to the peripheral mapping tables to understand completely the following informations). Should the present documentation be inadequate please refer to the component's manufacturer documentation.

# **RELAY OUTPUTS**

Input/Output registers OUT0 and OUT1 are used to perform the output management on **CI/O R16** board. The 8 bits of these registers have the following meaning:

D7 -> NO OUTn.7 D6 NO OUTn.6 -> D5 -> NO OUTn.5 D4 -> NO OUTn.4 D3 NO OUTn.3 -> NO OUTn.2 D2-> NO OUTn.1 D1 -> D0-> NO OUTn.0

The indication **NO OUTn.?** stands for OUT0 and OUT1 sections, whose output signals are available on connector CN2.

Performing an output operation at the address of OUT0 or OUT1 the corresponding eight outputs are set by the output data, while performing an input operation at the same address the status of the corresponding signals is input.

The correspondance between status of an output and value of a bit is:

Bit at logic 0 -> Output disabled = Realy contact open

Bit at logic 1 -> Output enabled = Realy contact closed

OUT0 and OUT1 registers are reset (all bits are 0) when a Reset or a Power On occour if **DSW1.1** is on, this disables all the outputs and opens all the relays contacts.

CI/O R16 Rel. 5.00 Page 21

# **OPTOCOUPLED INPUTS**

Input registers IN1 and IN2 are used to perform the input management on **CI/O R16** board. The 8 bits of these registers have the following meaning:

D7 -> INn.7 D6 INn.6 -> D5 INn.5 -> D4 INn.4 -> D3 INn.3 -> D2INn.2 -> INn.1 D1 -> D0INn.0 ->

The indication **INn.?** stands for IN1 and IN2 sections, whose input signals are available on connector CN1.

Performing an input operation at the address of IN1 or IN2 the corresponding eight optocoupled input signals are acquired.

The correspondance between status of an input and value of a bit is:

Bit at logic 0 -> Input disabled = Input contact open Bit at logic 1 -> Input enabled = Input contact closed

#### EXTERNAL CARIDS

**CI/O R16** board can interface to most of **grifo**® industrial boards. Their main purpose is to perform a digital Inpu/Output interfacement between CPU (**GPC**®) cards and the external world. Here is reported an illustrative list of cards capable to interact with **CI/O R16** board with a short description of their features; for further informations please request the specific documentation.

#### MB3 01-MB4 01-MB8 01

Mother Board 3, 4, 8 slots

Motherboard featuring 3, 4 or 8 slots of **ABACO**® industrial BUS; pitch 4 TE; standard power supply connectors; LEDs for visual feed-back of power supply; holes for rack docking.

#### SPB 04-SPB 08

Switch Power BUS 4-8 slots

Motherboard featuring 4-8 slots of **ABACO**<sup>®</sup> industrial BUS; pitch 4 TE; standard power supply connectors; termination resistances; connector type F for **SPC xxx** supply; holes for rack docking.

#### **ABB 03**

**ABACO®** Block BUS 3 slots

3 slots **ABACO**<sup>®</sup> mother board; 4 TE pitch connectors; **ABACO**<sup>®</sup> I/O BUS connector; screw terminal for power supply; connection for DIN C type and  $\Omega$  rails.

#### **ABB 05**

## **ABACO®** Block BUS 5 slots

5 slots **ABACO**<sup>®</sup> mother board with power supply. Double power supply built in; 5Vdc 2,5A section for powering the on board logic; second section at 24Vdc 400mA galvanically coupled, for the optocoupled input lines. Auxiliary connector for **ABACO**<sup>®</sup> I/O BUS. Connection for DIN  $\Omega$  rails.

#### **SBP 02-xx**

Switch BLOCK Power xx version

Low cost switching power supply able to generate voltage from +5 to +40 Vdc and current up to 2.5 A; Input from 12 to 24 Vac; Connection for DIN C Type and  $\Omega$  rails.

#### **SPC 03.5S**

Switch Power Card +5 Vdc

Europe format switching power supply capable to provide +5 Vdc to a load of 4 A; input voltage 12÷24 Vac; power-failure; connector for back-up battery; standard connector for mother board **SPB 0x**.

#### **SPC 512**

Switch Power Card +5 Vdc +12 Vdc

Europe format switching power supply capable to provide +5 Vdc 5A and +12 Vdc 2.5 A; input voltage 12÷24 Vac; power-failure; connector for back-up battery; standard connector for mother board **SPB 0x**.

CI/O R16 Rel. 5.00 ] — Page 23

#### GPC® 51

#### General Purpose Controller fam. 51

Microprocessor family 51 INTEL including the masked BASIC chip; the board features: 16 I/O TTL lines; dip switch; 3 timer/counter; RS 232; 4 A/D converter signals resolution 11 bit; buzzer; on board EPROM programmer; RTC and 32K SRAM with Lithium battery back up; controlloer for display and keyboard.

#### **GPC® 188F**

General Purpose Controller 80C188

$80C188~\mu P~20MHz;~1~RS~232~line;~1~RS~232,~RS~422-485~or~Current~Loop~line;~24~TTL~I/O~lines;~1M~EPROM~or~512K~FLASH;~1M~RAM~Lithium~battery~backed;~8K~serial~EEPROM;~RTC;~Watch~Dog;~8~Dip~switch;~3~Timer~Counter;~8~13~bit~A/D~lines;~Power~failure;~activity~LEDs;~single~power~supply~+5Vdc.$

#### GPC® 15A

General Purpose Controller 84C15

Full CMOS card, 10÷20 MHz 84C15 CPU; 512K EPROM or FLASH; 128K RAM; 8K RAM and RTC backed; 8K serial EEPROM; 1 RS 232 line; 1 RS 232 line or RS 422-485 or Current Loop line; 32 or 40 TTL I/O lines; CTC; Watch dog; 2 Dip switches; Buzzer.

#### GPC® 150

General Purpose Controller 84C15

Microprocessor Z80 at 16 MHz; implementation completely CMOS; 512K EPROM or FLASH; 512K SRAM; RTC; Back-Up through external Lithium battery; 4M serail FLASH; 1 serial line RS 232 plus 1 RS 232 or RS 422-485 or current loop; 40 I/O TTL; 2 timer/counter; 2 watch dog; dip switch; EEPROM; A/D converter with resolution 12 bit; activity LED.

#### GPC® 15R

General Purpose Controller 84C15

$84C15 \,\mu\text{P}$ ,  $10 \div 16 \,\text{MHz}$ ; 1 RS 232 line; 1 RS 232 or RS 422-485 or C. L. line;  $16 \div 24 \,\text{TTL}$  I/O lines; 16 Opto-in; 8 Relays; 4 Opto Coupled Timers Counters; 512K EPROM or FLASH; 512K RAM and RTC backed; 8K serial EEPROM; 8K Backed RAM modul; Buzzer; 1 Activity LED; Watch dog;  $4 \div 12 \,\text{readable DIPs}$ ; LCD Interface.

#### **GPC® 323**

General Purpose Controller 51 family

$80C32\,\mu P,\,14\,MHz;$  Full CMOS;  $1\,RS\,232\,line$  (software);  $1\,RS\,232\,or\,RS\,422-485\,or\,Current\,Loop\,line; <math>24\,TTL\,I/O\,lines;\,11\,A/D\,12\,bits\,lines;\,3\,Timers\,Counters;\,64K\,EPROM;\,64K\,RAM;\,32K\,RAM\,and\,RTC\,backed;\,32K\,DIL\,EEPROM;\,8K\,serial\,EEPROM;\,Buzzer;\,2\,Activity\,LED;\,Watch\,dog;\,5\,readable\,DIPs;\,LCD\,Interface.$

Page 24 — [ CI/O R16 Rel. 5.00

FIGURE 13: Possible connections diagram

CI/O R16 Rel. 5.00 ] — Page 25

#### **GPC® 553**

#### General Purpose Controller 80C552

$80C552 \,\mu\text{P}$ ,  $22 \div 33 \,\text{MHz}$ ; 1 RS 232 line (software); 1 RS 232 or RS 422-485 or Current Loop line; 16 TTL I/O lines; 8 A/D 10 bits lines; 3 Timers Counters; 64K EPROM; 64K RAM; 32K RAM and RTC backed; 32K DIL EEPROM; 8K serial EEPROM; 2 PWM lines; 1 Activity LED; Watch dog; 5 readable DIPs; LCD Interface.

#### **GPC® 153**

General Purpose Controller Z80

$84C15\,\mu P$ ,  $10\div16\,MHz$ ; Full CMOS; 1 RS 232 line; 1 RS 232 or RS 422-485 or Current Loop line; 16 TTL I/O lines; 8 A/D 12 bits lines; 2÷4 Timers Counters; 512K EPROM or FLASH; 512K RAM and RTC backed; 8K serial EEPROM; Buzzer; 1 Activity LED; Watch dog; 8 readable DIPs; LCD Interface.

#### **GPC® 183**

General Purpose Controller Z180

$Z180\,\mu P$ ,  $10\div16\,MHz$ ; Full CMOS; 1 RS 232 line; 1 RS 232 or RS 422-485 or Current Loop line; 24 TTL I/O lines; 11 A/D 12 bits lines; 2 Timers Counters; 512K EPROM or FLASH; 512K RAM and RTC backed; 8K serial EEPROM; Buzzer; 2 Activity LED; Watch dog; 4 readable DIPs; LCD Interface.

#### **GPC® 324/D**

"4" Type General Purpose Controller 80C32/320

80C32 or 80C320 µP,  $14 \div 22$  MHz; Full CMOS; 1 RS 232 line; 1 RS 232 or RS 422-485 or Current Loop line;  $4 \div 16$  TTL I/O lines; 3 Timers Counters; 64K EPROM; 64K RAM; 32K RAM backed; 32K DIL E2; 8K serial EEPROM; Watch dog; 1 readable DIP; LCD Interface; Abaco® I/O BUS; 5Vdc Power supply; Size: 100x50 mm.

#### **GPC®** 554

General Purpose Controller 80C552

Microprocessor 80C552 at 22 MHz; implementation completely CMOS; 32K EPROM; 32 K SRAM; 32 K EEPROM or SRAM; EEPROM; 2 RS 232 serial lines; 16 I/O TTL; 2 PWM lines; 16 bits Timer/Counter; Watch Dog; 6 signals A/D converter with resolution 10 bit; interface for **ABACO**® I/O BUS.

#### **GPC® 154**

"4" Type General Purpose Controller Z80

$84C15\,\mu\text{P}$ ,  $10\div16\,\text{MHz}$ ; Full CMOS;  $1\,\text{RS}\,232\,\text{line}$ ;  $1\,\text{RS}\,232\,\text{or}\,\text{RS}\,422\text{-}485\,\text{line}$ ;  $16\,\text{TTL}\,\text{I/O}\,\text{lines}$ ;  $2\div4\,\text{Timers}\,\text{Counters}$ ;  $512K\,\text{EPROM}\,\text{or}\,\text{FLASH}$ ;  $512K\,\text{RAM}\,\text{and}\,\text{RTC}\,\text{backed}$ ;  $8K\,\text{serial}\,\text{EEPROM}$ ; Watch dog;  $2\,\text{readable}\,\text{DIPs}$ ; LCD Interface; Abaco® I/O BUS;  $5Vdc\,\text{Power}\,\text{supply}$ ; Size:  $100x50\,\text{mm}$ .

Page 26 — CI/O R16 Rel. 5.00

#### **GPC® 884**

#### General Purpose Controller Am188ES

Microprocessor AMD Am188ES up to 40 MHz16 bits; implementation completely CMOS; serie 4 format; 512K EPROM or FLASH; 512K SRAM backed with Lithium battery; RTC; 1 RS 232 serial line + 1 RS 232 or RS 422-485 or current loop; 16 I/O TTL; 3 timer/counter; watch dog; EEPROM; 11 signals A/D converter with 12 bit resolution; interface for **ABACO**® I/O BUS.

#### **GPC® 114**

## General Purpose Controller 68HC11

Microprocessor 68HC11A1 at 8 MHz; implementation completely CMOS; serie 4 format; 32K EPROM; 32K SRAM backed with Lithium battery; 32K EPROM, SRAM, EEPROM; RTC; 1 serial line RS 232 or RS 422-485; 10 I/O TTL; 3 timer/counter; watch dog; 8 signals A/D converter with resolution 8 bit; 1 asunchronous serial line; extremly low power consumption; interface for **ABACO**® I/O BUS.

#### **PBI 01**

# PNP BLOCK Input

Interface for PNP drivers through NPN inputs; 16 inputs for driver PNP, visualized by LEDs; 16 NPN outputs on **ABACO**® standard input connector; Plastic mount for rails DIN 46277-1 and 3.

#### **FBC 20-120**

Flat Block Contact 20 vie

Interface for 2 or 1 mounting cable connectors (low profile 20 pins male) and quick release screw terminal connectors; Plastic mount for rails DIN 46277-1 and 3.

#### **FBC 34**

Flat Block Contact 34 vie

Interface for 2 mounting cable connector (low profile 34 pins male) and quick release screw terminal connectors; Plastic mount for rails DIN 46277-1 and 3.

### FBC L20

Flat Block Contact LED 20 vie

Interface for 1 mounting cable connector (low profile 20 pins male, featuring **ABACO**® standard Input pin out, and quick release screw terminal connectors; All the signals are visualized through LEDs; Plastic mount for rails DIN 46277-1 and 3.

#### FBC L34

Flat Block Contact LED 34 vie

Interface for 2 mounting cable connectors (low profile34 and 20 pins male) and quick release screw terminal connectors; featuring **ABACO**® standard Input and Output pin out; All the signals are visualized through LEDs; Plastic mount for rails DIN 46277-1 and 3.

# BIBLIOGRAPHY

Here follows a list of manuals and technical notes that the User can read to acquire more informations about **CI/O R16** board.

Manual SGS-THOMSON: Industrial and Computer Peripheral ICs - Data Book

Manual TEXAS INSTRUMENTS: The TTL data Book - SN54/74 Families

Manual TOSHIBA: Photo Couplers - Data Book

Please connect to the manifactures Web sites to get the latest version of all manuals and data sheets.

# APPENDIX A: ALPHABETICAL INDEX

$\mathbf{A}$

**ABACO®** BUS 4, 12, 19

B

BOARD MAPPING 19

$\mathbf{C}$

CARD VERSION 1

CONNECTIONS 8

CONNECTOR FOR ABACO® BUS 12

CONNECTOR FOR OPTOCOUPLED INPUTS 8

CONNECTORS 7

CN1 8

CN2 10

K1 **12**

CONTROL LOGIC 4

CURRENT CONSUMPTION 6

D

DSW1 4, 14, 19

$\mathbf{E}$

ELECTRIC FEATURES 6

EXTERNAL CARDS 23

$\mathbf{F}$

FILTER 2, 6

$\mathbf{G}$

GENERAL INFORMATIONS 2

H

HARDWARE DESCRIPTION 19

I

I/O CONNNECTIONS 16

INPUT SECTION 4

INSTALLATION 8

INTERFACING AND ADDRESSING SECTION 4

WEIGHT 7

$\mathbf{W}$