# **PRELIMINARY DOCUMENTATION AAC 06** (Axis Acquisition Card 6 counter)

-იხიc-o\_\_\_●•<sup>®</sup>)(ხυ /) \_\_\_\_\_ grifo<sup>®</sup> -

ITALIAN TECHNOLOGY

#### K1 - CONNECTOR FOR ABACO<sup>®</sup> BUS

K1 is a 64 pins, male, 90°, DIN 41612 connector with 2.54 pitch.

On K1 are available all the industrial **ABACO**<sup>®</sup> BUS signals and it can be used for connections to many other peripheral cards. In the table below there are the standard pin outs both for 8 bits and 16 bits CPU and the signal connected on **ACC 06**. All signals follow TTL standard.

| Α           | Α          | Α      | PIN | С             | С          | С           |

|-------------|------------|--------|-----|---------------|------------|-------------|

| 16 bits BUS | 8 bits BUS | AAC 06 |     | <b>AAC 06</b> | 8 bits BUS | 16 bits BUS |

| GND         | GND        | GND    | 1   | GND           | GND        | GND         |

| +5 Vdc      | +5 Vdc     | +5 Vdc | 2   | +5 Vdc        | +5 Vdc     | +5 Vdc      |

| D0          | D0         | D0     | 3   | N.C.          |            | D8          |

| D1          | D1         | D1     | 4   | N.C.          |            | D9          |

| D2          | D2         | D2     | 5   | N.C.          |            | D10         |

| D3          | D3         | D3     | 6   | N.C.          | /INT       | /INT        |

| D4          | D4         | D4     | 7   | N.C.          | /NMI       | /NMI        |

| D5          | D5         | D5     | 8   | N.C.          | /HALT      | D11         |

| D6          | D6         | D6     | 9   | N.C.          | /MREQ      | /MREQ       |

| D7          | D7         | D7     | 10  | /IORQ         | /IORQ      | /IORQ       |

| A0          | A0         | A0     | 11  | /RD           | /RD        | /RDLDS      |

| A1          | A1         | A1     | 12  | /WR           | /WR        | /WRLDS      |

| A2          | A2         | A2     | 13  | N.C.          | /BUSAK     | D12         |

| A3          | A3         | A3     | 14  | N.C.          | /WAIT      | /WAIT       |

| A4          | A4         | A4     | 15  | N.C.          | /BUSRQ     | D13         |

| A5          | A5         | A5     | 16  | /RESET        | /RESET     | /RESET      |

| A6          | A6         | A6     | 17  | /M1           | /M1        | /IACK       |

| A7          | A7         | A7     | 18  | N.C.          | /RFSH      | D14         |

| A8          | A8         | N.C.   | 19  | N.C.          | /MEMDIS    | /MEMDIS     |

| A9          | A9         | N.C.   | 20  | N.C.          | VDUSEL     | A22         |

| A10         | A10        | N.C.   | 21  | N.C.          | /IEI       | D15         |

| A11         | A11        | N.C.   | 22  | N.C.          |            |             |

| A12         | A12        | N.C.   | 23  | N.C.          | CLK        | CLK         |

| A13         | A13        | N.C.   | 24  | N.C.          |            | /RDUDS      |

| A14         | A14        | N.C.   | 25  | N.C.          |            | /WRUDS      |

| A15         | A15        | N.C.   | 26  | N.C.          |            | A21         |

| A16         |            | N.C.   | 27  | N.C.          |            | A20         |

| A17         |            | N.C.   | 28  | N.C.          |            | A19         |

| A18         |            | N.C.   | 29  | N.C.          | /R.T.      | /R.T.       |

| +12 Vdc     | +12 Vdc    | N.C.   | 30  | N.C.          | -12 Vdc    | -12 Vdc     |

| +5 Vdc      | +5 Vdc     | +5 Vdc | 31  | +5 Vdc        | +5 Vdc     | +5 Vdc      |

| GND         | GND        | GND    | 32  | GND           | GND        | GND         |

FIGURE 1: K1 - ABACO® BUS CONNECTOR

AAC 06

Signals description:

8 bits CPU

| A0-A15      | =   | 0   | - Address BUS             |

|-------------|-----|-----|---------------------------|

| D0-D7       | _   | I/O |                           |

|             |     |     |                           |

| /INT        | =   | I   | - Interrupt request       |

| /NMI        | =   | Ι   | - Non Maskable Interrupt  |

| /HALT       | =   | 0   | - Halt state              |

| /MREQ       | =   | 0   | - Memory Request          |

| /IORQ       | =   | 0   | - Input Output Request    |

| /RD         | =   | 0   | - Read cycle status       |

| /WR         | =   | 0   | - Write cycle status      |

| /BUSAK      | =   | 0   | - BUS Acknowledge         |

| /WAIT       | =   | Ι   | - Wait                    |

| /BUSRQ      | =   | Ι   | - BUS Request             |

| /RESET      | =   | 0   | - Reset                   |

| /M1         | =   | 0   | - Machine cycle one       |

| /RFSH       | =   | 0   | - Refresh for dynamic RAM |

| /MEMDIS     | 5 = | Ι   | - Memory Display          |

| /VDUSEL     | =   | Ο   | - VDU Selection           |

| /IEI        | =   | Ι   | - Interrupt Enable Input  |

| CLK         | =   | 0   | - System clock            |

| <b>R.T.</b> | =   | Ι   | - Reset button            |

| +5 Vdc      | =   | Ι   | - Power supply at +5 Vdc  |

| +12 Vdc     | =   | Ι   | - Power supply at +12 Vdc |

| -12 Vdc     | =   | Ι   | - Power supply at -12 Vdc |

| GND         | =   |     | - Ground signal           |

|             |     |     |                           |

16 bits CPU

| A16-A22 | = | 0   | - Address BUS             |

|---------|---|-----|---------------------------|

| D8-D15  | = | I/O | - Data BUS                |

| /RD UDS | = | 0   | - Read Upper Data Strobe  |

| /WR UDS | = | 0   | - Write Upper Data Strobe |

| /IACK   | = | 0   | - Interrupt Acknowledge   |

| /RD LDS | = | 0   | - Read Lower Data Strobe  |

| /WR LDS | = | 0   | - Write Lower Data Strobe |

|         |   |     |                           |

| N. C.   | = |     | - Not Connected           |

# NOTE

Directionality indications as above stated are referred to a master (GPC®) board and have been kept untouched to avoid ambiguity in case of multi-boards systems.

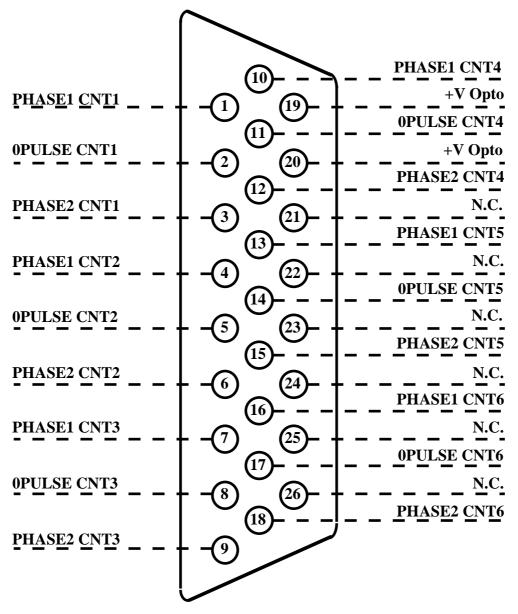

#### **CN1 - CONNECTOR FOR COUNTER INPUTS**

CN1 is a 26 pins, female, 90°, high density D connector.

It is placed on the front side of the card and it is used to connect the inputs of the six counters, each one of these is provided of three optocoupled signals, NPN type.

The power supply of all these inputs can be +12 Vdc or +24 Vdc according with proper jumpers configurations, as described in the following paragraphs.

FIGURE 2: CN1 CONNECTOR FOR COUNTER INPUTS

Signals description:

| PHASE1 CNTn        | = I - Phase 1 input signal for counter n.                            |

|--------------------|----------------------------------------------------------------------|

| PHASE2 CNTn        | = I - Phase 2 input signal for counter n.                            |

| <b>0PULSE CNTn</b> | = I - Zero pulse input signal for counter n.                         |

| +V Opto            | = I - Gavanically insulated voltage for optocoupled NPN inputs power |

|                    | supply.                                                              |

| N.C.               | = - Not connected.                                                   |

|                    |                                                                      |

Page 4

AAC 06

Rel. 5.00

# JUMPERS

On AAC 06 there are 32 jumpers for card configuration. Connecting these jumpers, the user can define for example the counters connections, the external power supply type and so on. Below there is the jumpers list complete of relative functions:

| JUMPER | POSITION   | FUNCTION                                                                                                                       |

|--------|------------|--------------------------------------------------------------------------------------------------------------------------------|

| J1     | 1-2<br>2-3 | The card manages the signal /M1 available on K1 (pin 17C)<br>The card doesn't manages the signal /M1 available on K1 (pin 17C) |

| J2     | 1-2        | It connects PHASE1 CNT4 to signal for counting up (increment) of counter 4                                                     |

|        | 2-3        | It connects PHASE1 CNT4 to signal for measuring with direction discriminator of counter 4                                      |

| J3     | 1-2        | It connects PHASE2 CNT4 to signal for counting down (decrement of counter 4                                                    |

|        | 2-3        | It connects PHASE2 CNT4 to signal for measuring with direction discriminator of counter 4                                      |

| J4     | 1-2        | It connects the overflow signal of counter 4 to signal for counting up (increment) of counter 5                                |

|        | 2-3        | It connects PHASE1 CNT5 to signal for counting up (increment) of counter 5                                                     |

|        | 3-4        | It connects PHASE1 CNT5 to signal for measuring with direction discriminator of counter 5                                      |

| J5     | 1-2        | It connects the underflow signal of counter 4 to signal for counting down (decrement) of counter 5                             |

|        | 2-3        | It connects PHASE2 CNT5 to signal for counting down (decrement<br>of counter 5                                                 |

|        | 3-4        | It connects PHASE2 CNT5 to signal for measuring with direction discriminator of counter 5                                      |

| J6     | 1-2        | It connects PHASE1 CNT6 to signal for counting up (increment) of counter 6                                                     |

|        | 2-3        | It connects PHASE1 CNT6 to signal for measuring with direction discriminator of counter 6                                      |

| J7     | 1-2        | It connects PHASE2 CNT6 to signal for counting down (decremen of counter 6                                                     |

|        | 2-3        | It connects PHASE2 CNT6 to signal for measuring with direction discriminator of counter 6                                      |

| <u>-ab-ac-</u> | ••®(bu/)                | grifo <sup>®</sup>                                                           |                              |

|----------------|-------------------------|------------------------------------------------------------------------------|------------------------------|

| J8             | 1-2                     | It connects PHASE1 CNT1 to signal for of counter 1                           | pr counting up (increment)   |

|                | 2-3                     | It connects PHASE1 CNT1 to signal for discriminator of counter 1             | or measuring with direction  |

| J9             | 1-2                     | It connects PHASE2 CNT1 to signal fo of counter 1                            | r counting down (decremer    |

|                | 2-3                     | It connects PHASE2 CNT1 to signal for discriminator of counter 1             | or measuring with direction  |

| J10            | 1-2                     | It connects the overflow signal of coun<br>up (increment) of counter 2       | ter 1 to signal for counting |

|                | 2-3                     | It connects PHASE1 CNT2 to signal for<br>of counter 2                        | or counting up (increment)   |

|                | 3-4                     | It connects PHASE1 CNT2 to signal for discriminator of counter 2             | or measuring with direction  |

| J11            | 1-2                     | It connects the underflow signal of cou<br>down (decrement) of counter 2     | nter 4 to signal for countin |

|                | 2-3                     | It connects PHASE2 CNT2 to signal fo of counter 2                            | r counting down (decreme     |

|                | 3-4                     | It connects PHASE2 CNT2 to signal for discriminator of counter 2             | or measuring with direction  |

| J12            | 1-2                     | It connects PHASE1 CNT3 to signal for of counter 3                           | or counting up (increment)   |

|                | 2-3                     | It connects PHASE1 CNT3 to signal for discriminator of counter 3             | or measuring with direction  |

| J13            | 1-2                     | It connects PHASE2 CNT3 to signal fo of counter 3                            | r counting down (decreme     |

|                | 2-3                     | It connects PHASE2 CNT3 to signal for discriminator of counter 3             | or measuring with direction  |

| J14            | not connected           | It doesn't connect the metallic shield of ground signal (GND)                | CN1 to power supply          |

|                | connected               | It connects the metallic shield of CN1 t<br>signal (GND)                     | o power supply ground        |

| J15            | not connected connected | It configures PHASE2 CNT6 signal for<br>It configures PHASE2 CNT6 signal for |                              |

| J16            | not connected connected | It configures OPULSE CNT6 signal fo<br>It configures OPULSE CNT6 signal fo   |                              |

| J17            | not connected connected | It configures PHASE1 CNT6 signal for<br>It configures PHASE1 CNT6 signal for | 1 110                        |

ITALIAN TECHNOLOGY \_\_\_\_\_\_ grifo<sup>®</sup> \_\_\_\_\_

buı

| J18 | not connected connected | It configures PHASE2 CNT5 signal for +24 Vdc power supply<br>It configures PHASE2 CNT5 signal for +12 Vdc power supply |

|-----|-------------------------|------------------------------------------------------------------------------------------------------------------------|

| J19 | not connected connected | It configures OPULSE CNT5 signal for +24 Vdc power supply<br>It configures OPULSE CNT5 signal for +12 Vdc power supply |

| J20 | not connected connected | It configures PHASE1 CNT5 signal for +24 Vdc power supply<br>It configures PHASE1 CNT5 signal for +12 Vdc power supply |

| J21 | not connected connected | It configures PHASE2 CNT4 signal for +24 Vdc power supply<br>It configures PHASE2 CNT4 signal for +12 Vdc power supply |

| J22 | not connected connected | It configures OPULSE CNT4 signal for +24 Vdc power supply<br>It configures OPULSE CNT4 signal for +12 Vdc power supply |

| J23 | not connected connected | It configures PHASE1 CNT4 signal for +24 Vdc power supply<br>It configures PHASE1 CNT4 signal for +12 Vdc power supply |

| J24 | not connected connected | It configures PHASE2 CNT3 signal for +24 Vdc power supply<br>It configures PHASE2 CNT3 signal for +12 Vdc power supply |

| J25 | not connected connected | It configures OPULSE CNT3 signal for +24 Vdc power supply<br>It configures OPULSE CNT3 signal for +12 Vdc power supply |

| J26 | not connected connected | It configures PHASE1 CNT3 signal for +24 Vdc power supply<br>It configures PHASE1 CNT3 signal for +12 Vdc power supply |

| J27 | not connected connected | It configures PHASE2 CNT2 signal for +24 Vdc power supply<br>It configures PHASE2 CNT2 signal for +12 Vdc power supply |

| J28 | not connected connected | It configures OPULSE CNT2 signal for +24 Vdc power supply<br>It configures OPULSE CNT2 signal for +12 Vdc power supply |

| J29 | not connected connected | It configures PHASE1 CNT2 signal for +24 Vdc power supply<br>It configures PHASE1 CNT2 signal for +12 Vdc power supply |

| J30 | not connected connected | It configures PHASE2 CNT1 signal for +24 Vdc power supply<br>It configures PHASE2 CNT1 signal for +12 Vdc power supply |

| J31 | not connected connected | It configures OPULSE CNT1 signal for +24 Vdc power supply<br>It configures OPULSE CNT1 signal for +12 Vdc power supply |

| J32 | not connected connected | It configures PHASE1 CNT1 signal for +24 Vdc power supply<br>It configures PHASE1 CNT1 signal for +12 Vdc power supply |

#### FIGURE 3: JUMPERS FUNCTIONS TABLE

The jumper J1 must be connected in position 1-2 when the CPU card, that controls the **AAC 06**, is based on Z80 or compatible CPU, to avoid malfunction especially during the interrupts management performed by same CPU card.

- arifo® -

The connection of input signals to signals for measuring with direction discriminator allows a comfortable acquisition of bidirectional encoders, obtaining by the card an absolute combination that coincides with the current encoder position, without any intermediate calculations.

Instead the connection of input signals to signal for counting up (increment and/or down (decrement) allows the development of simple counters, frequency measurement, period measurement, up and down pulse counter, etc.

Finally the counters 1, 2 and 3, 4 can be cascade connected obtaining total 32 bits counters. For example if you want to use counter 1 and 2 in cascade, you must:

- connect the signal to measure to counter 1 inputs: PHASE1 CNT1, PHASE2 CNT1 and 0PULSE CNT1;

- connect the jumpers J8 and J9 in position 1-2 or 2-3 according with direction disriminator necessity;

- connect the jumpers J10 and J11 in position 1-2 obtaining that the overflow and underflow of counter 1 increase and decrease the counter 2;

- acquire the 4 counting registers and calculate the total 32 bits combination by using the couple of byte from counter 1 (these are the 16 less significant bits) and the couple from counter 2 (the 16 most significant bits).

If the jumper J14 is closed, the card power supply ground (GND on K1) is connected with metallic frame of CN1 connector obtaining an electric shielding on input signals. Please pay attention on this jumper connection in fact when the external connections is not performed with the proper noisy immunity techniques, it carries troubles on power supply of the entire system.

When the jumpers J15  $\div$ J32 are connected it is possible to connect a +V Opto = +12 Vdc while if they are open the +V Opto is +24 Vdc. On CN1 connector there is only one +V Opto signal, so if you must contemporaneously acquire both +12 Vdc and +24 Vdc inputs please ensure separation of all the ground signals of the same input signals, in fact the positive signals must be linked together and then connected to pins 19 and 20 of CN1.

# **COUNTER FUNCTIONALITY CONFIGURATIONON**

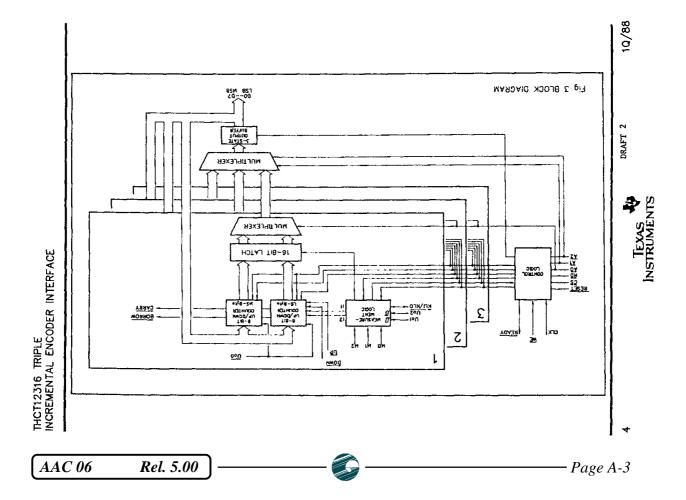

The card **AAC 06** is based on two THCT 12316 components that are triple programmable counter that can operate in 8 different modes. For detailed information about these modalities please refer to appendix A of the manual, while for the mode selection the user must configure three dip switches DIP2, DIP3, DIP4 as below described:

| DIP 4.3<br>ON<br>ON<br>ON<br>OFF<br>OFF<br>OFF<br>OFF | DIP 4.2<br>ON<br>ON<br>OFF<br>OFF<br>ON<br>ON<br>OFF<br>OFF  | DIP 4.1<br>ON<br>OFF<br>ON<br>OFF<br>ON<br>OFF<br>ON<br>OFF | -><br>-><br>-><br>-><br>-><br>-><br>-> | MODE<br>Mode 0 for counter 1<br>Mode 1 for counter 1<br>Mode 2 for counter 1<br>Mode 3 for counter 1<br>Mode 4 for counter 1<br>Mode 5 for counter 1<br>Mode 6 for counter 1<br>Mode 7 for counter 1 |

|-------------------------------------------------------|--------------------------------------------------------------|-------------------------------------------------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIP 4.6<br>ON<br>ON<br>ON<br>OFF<br>OFF<br>OFF<br>OFF | DIP 4.5<br>ON<br>OFF<br>OFF<br>OFF<br>ON<br>ON<br>OFF<br>OFF | DIP 4.4<br>ON<br>OFF<br>ON<br>OFF<br>ON<br>OFF<br>ON<br>OFF | -><br>-><br>-><br>-><br>-><br>-><br>-> | MODE<br>Mode 0 for counter 2<br>Mode 1 for counter 2<br>Mode 2 for counter 2<br>Mode 3 for counter 2<br>Mode 4 for counter 2<br>Mode 5 for counter 2<br>Mode 6 for counter 2<br>Mode 7 for counter 2 |

|                                                       |                                                              |                                                             |                                        |                                                                                                                                                                                                      |

| DIP 3.2<br>ON<br>ON<br>ON<br>OFF<br>OFF<br>OFF<br>OFF | DIP 4.8<br>ON<br>OFF<br>OFF<br>OFF<br>ON<br>ON<br>OFF<br>OFF | DIP 4.7<br>ON<br>OFF<br>ON<br>OFF<br>ON<br>OFF<br>ON<br>OFF | -><br>-><br>-><br>-><br>-><br>-><br>-> | MODE<br>Mode 0 for counter 3<br>Mode 1 for counter 3<br>Mode 2 for counter 3<br>Mode 3 for counter 3<br>Mode 4 for counter 3<br>Mode 5 for counter 3<br>Mode 6 for counter 3<br>Mode 7 for counter 3 |

| -9696   | <b>;•</b> •••• | <b>bu</b> / — |    | — grifo <sup>®</sup> — |  |

|---------|----------------|---------------|----|------------------------|--|

| DIP 2.6 | DIP 2.5        | DIP 2.4       |    | MODE                   |  |

| ON      | ON             | ON            | -> | Mode 0 for counter 5   |  |

| ON      | ON             | OFF           | -> | Mode 1 for counter 5   |  |

| ON      | OFF            | ON            | -> | Mode 2 for counter 5   |  |

| ON      | OFF            | OFF           | -> | Mode 3 for counter 5   |  |

| OFF     | ON             | ON            | -> | Mode 4 for counter 5   |  |

| OFF     | ON             | OFF           | -> | Mode 5 for counter 5   |  |

| OFF     | OFF            | ON            | -> | Mode 6 for counter 5   |  |

| OFF     | OFF            | OFF           | -> | Mode 7 for counter 5   |  |

| DIP 3.1 | DIP 2.8        | DIP 2.7       |    | MODE                   |  |

| ON      | ON             | ON            | -> | Mode 0 for counter 6   |  |

| ON      | ON             | OFF           | -> | Mode 1 for counter 6   |  |

| ON      | OFF            | ON            | -> | Mode 2 for counter 6   |  |

| ON      | OFF            | OFF           | -> | Mode 3 for counter 6   |  |

| OFF     | ON             | ON            | -> | Mode 4 for counter 6   |  |

| OFF     | ON             | OFF           | -> | Mode 5 for counter 6   |  |

| OFF     | OFF            | ON            | -> | Mode 6 for counter 6   |  |

| OFF     | OFF            | OFF           | -> | Mode 7 for counter 6   |  |

|         |                |               |    |                        |  |

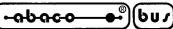

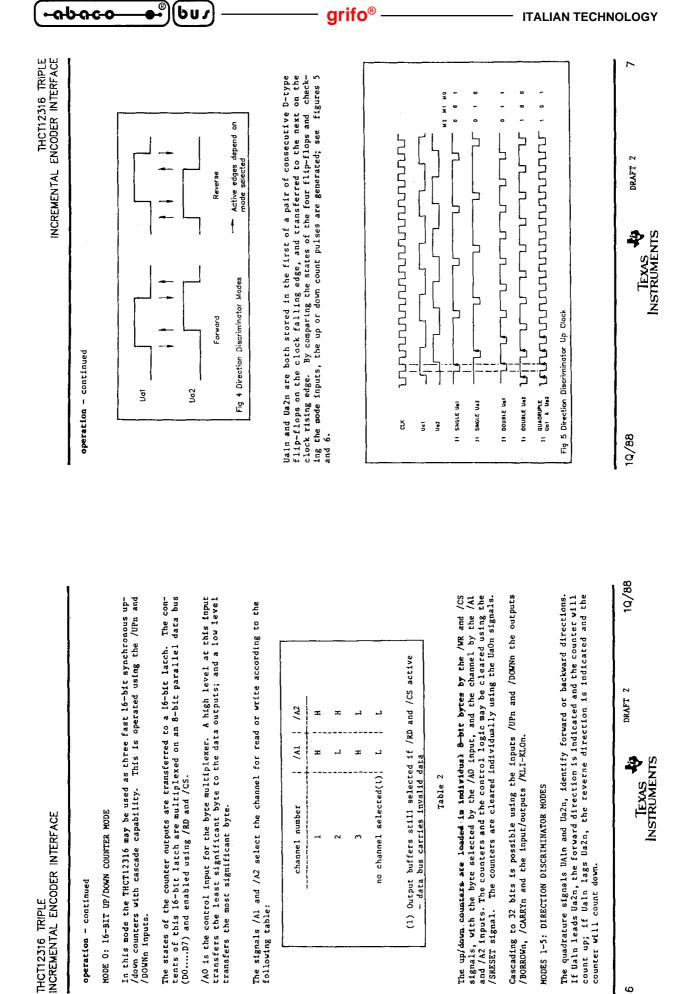

Below it is described a short description of the 8 function madalities, related to signals available on CN1 connector.

- Mode 0: COUNTER with increment or decrement (up or down) caused by PHASE1 CNTn and/or PHASE2 CNTn signals, without direction discriminator.

- Mode 1: DIRECTION DISCRIMINATOR of a single count pulse synchronous with PHASE1 CNTn rising in forward direction and falling in backward direction.

- Mode 2: DIRECTION DISCRIMINATOR of a single count pulse synchronous with PHASE2 CNTn rising in forward direction and falling in backward direction.

- Mode 3: DIRECTION DISCRIMINATOR of a double count pulse synchronous with PHASE1 CNTn rising and falling.

- Mode 4: DIRECTION DISCRIMINATOR of a double count pulse synchronous with PHASE2 CNTn rising and falling.

- Mode 5: DIRECTION DISCRIMINATOR of a quadruple count pulse synchronous with all edges.

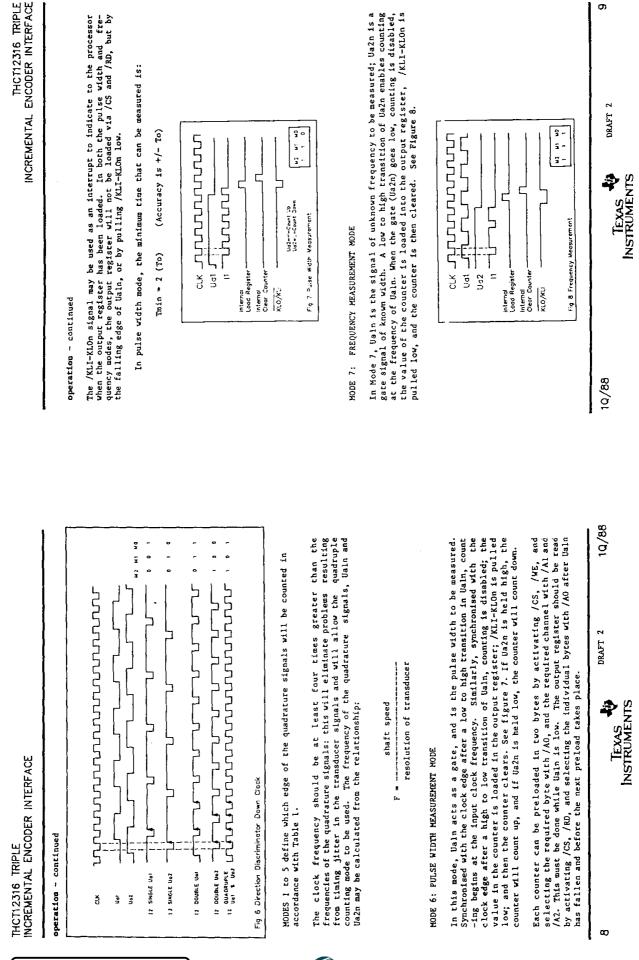

- Mode 6: PULSE WIDHT MEASUREMENT where PHASE1 CNTn is the gate signal and PHASE2 CNTn is high for up counting and low for down counting. Count is synchronous with rising clock.

- Mode 7: FREQUENCY MEASUREMENT where PHASE1 CNTn is frequency signal to be measured and PHASE2 CNTn is the gate signals of know time interval. Count is synchronous with rising edge of PHASE1 CNT n.

# VISUAL FEEDBACK

| LEDs | COLOUR | FUNCTION                               |

|------|--------|----------------------------------------|

| DL1  | Red    | Visualizes status of PHASE1 CNT1 line. |

| DL9  | Green  | Visualizes status of PHASE2 CNT1 line. |

| DL7  | Yellow | Visualizes status of 0PULSE CNT1 line. |

| DL2  | Red    | Visualizes status of PHASE1 CNT2 line. |

| DL10 | Green  | Visualizes status of PHASE2 CNT2 line. |

| DL17 | Yellow | Visualizes status of 0PULSE CNT2 line. |

| DL3  | Red    | Visualizes status of PHASE1 CNT3 line. |

| DL11 | Green  | Visualizes status of PHASE2 CNT3 line. |

| DL8  | Yellow | Visualizes status of 0PULSE CNT3 line. |

| DL4  | Red    | Visualizes status of PHASE1 CNT4 line. |

| DL12 | Green  | Visualizes status of PHASE2 CNT4 line. |

| DL15 | Yellow | Visualizes status of 0PULSE CNT4 line. |

| DL5  | Red    | Visualizes status of PHASE1 CNT5 line. |

| DL13 | Green  | Visualizes status of PHASE2 CNT5 line. |

| DL18 | Yellow | Visualizes status of 0PULSE CNT5 line. |

| DL6  | Red    | Visualizes status of PHASE1 CNT6 line. |

| DL14 | Green  | Visualizes status of PHASE2 CNT6 line. |

| DL16 | Yellow | Visualizes status of 0PULSE CNT6 line. |

On the front side of **AAC 06** board, there are two rows of eight LEDs plus other two LEDs that visualize the input signals status conditions, as described in the following table:

grifo<sup>®</sup> -

-abaco

bus

#### FIGURE 4: VISUAL FEEDBACK TABLE

Each LED is enabled when the relative input signal is active that is when the pin on CN1 connector is connected to ground signal of insulated inputs power supply (= reference of +V Opto).

### **BOARD MAPPING**

AAC 06 board is mapped into a 16 consecutive I/O bytes addressing space that can be based starting from different base addresses according to how the board is configured. This feature allows to use several AAC 06 cards on the same ABACO<sup>®</sup> BUS, or to install them on a BUS where other peripheral cards are installed obtaining a structure that can be expanded without any difficulty or modifications to the application software.

The base address can be defined through the specific BUS interface circuitry on the board itself; this circuitry uses one dip switch, featuring 4 pins, from which it reads the address set by the user. Here follows the corrispondance between dip switches configuration and address signals.

| <b>DIP1.1</b> | -> | Address BUS signal A4 |

|---------------|----|-----------------------|

| <b>DIP1.2</b> | -> | Address BUS signal A5 |

| <b>DIP1.3</b> | -> | Address BUS signal A6 |

| <b>DIP1.4</b> | -> | Address BUS signal A7 |

These dip switches are driven in complemented logic, this means that if a switch is **ON** it generates a **logic zero**, viceversa if a switch is **OFF** it generates a **logic one**.

Also jumper J1 affects the addressing section and must be set according to the type of master control board (**CPU** or **GPC®**) used to drive the **AAC 06**. In detail if the master control board is provided with signal /M1 on **ABACO® BUS** connector, then jumper J1 must be connected in position 1-2 and viceversa.

To facilitate the board use here follow two mapping examples:

If the user has to map the board starting from base address 040H, driven by a master control card provided with the signal /M1, jumper and dip swithces status must be as follows:

| -> | Position 1-2   |

|----|----------------|

| -> | ON             |

| -> | ON             |

| -> | OFF            |

| -> | ON             |

|    | -><br>-><br>-> |

If the user has to map the board starting from base address F0H, driven by a master control card not provided with the signal /M1, jumper and dip swithces status must be as follows:

| J1            | -> | Position 2-3 |

|---------------|----|--------------|

| <b>DIP1.1</b> | -> | OFF          |

| <b>DIP1.2</b> | -> | OFF          |

| <b>DIP1.3</b> | -> | OFF          |

| DIP1.4        | -> | OFF          |

To easily locate the dip swithces, please refer card serigraph.

# grifo<sup>®</sup> -

### **INTERNAL REGISTERS ADDRESSING**

Indicating the board base address with **<baseaddr**>, that is the address set using DIP1, as indicated in the previous paragraph, **AAC 06** internal registers are addressable as explained in the following table.

| DEVICE        | REG.  | ADDRESS                   | R/W | MEANING                         |

|---------------|-------|---------------------------|-----|---------------------------------|

|               | CNT3H | <baseaddr>+02H</baseaddr> | R/W | Read/Set High byte of counter 3 |

|               | CNT3L | <baseaddr>+03H</baseaddr> | R/W | Read/Set Low byte of counter 3  |

| THCT<br>12316 | CNT2H | <baseaddr>+04H</baseaddr> | R/W | Read/Set High byte of counter 2 |

| IC8           | CNT2L | <baseaddr>+05H</baseaddr> | R/W | Read/Set Low byte of counter 2  |

|               | CNT1H | <baseaddr>+06H</baseaddr> | R/W | Read/Set High byte of counter 1 |

|               | CNT1L | <baseaddr>+07H</baseaddr> | R/W | Read/Set Low byte of counter 1  |

|               | CNT6H | <baseaddr>+0AH</baseaddr> | R/W | Read/Set High byte of counter 6 |

|               | CNT6L | <baseaddr>+0BH</baseaddr> | R/W | Read/Set Low byte of counter 6  |

| THCT<br>12316 | CNT5H | <baseaddr>+0CH</baseaddr> | R/W | Read/Set High byte of counter 5 |

| IC7           | CNT5L | <baseaddr>+0DH</baseaddr> | R/W | Read/Set Low byte of counter 5  |

|               | CNT4H | <baseaddr>+0EH</baseaddr> | R/W | Read/Set High byte of counter 4 |

|               | CNT4L | <baseaddr>+0FH</baseaddr> | R/W | Read/Set Low byte of counter 4  |

#### FIGURE 5: INTERNAL REGISTERS ADDRESSES TABLE

If using several boards on the same **ABACO<sup>®</sup> BUS**, when setting the boards mapping address the user shold be careful not to allocate more than one board in the same addressing space (consider the base address plus the bytes taken by the board addressing). If this condition is not satisfied a BUS conflict situation will occour, prejudicing the correct working of the whole system.

# TRIPLE COUNTER THCT 12316 AND COMPATIBLE

For the desctription of this triple counter please refer to the specific technical documentation in the appendix A of this manual and to description available in COUNTER FUNCTIONALITY CONFIGURATION. The information reported in appendix use different names for the input signals with the following corrispondence:

| Ualn | -> | PHASE1 CNTn        |

|------|----|--------------------|

| Ua2n | -> | PHASE2 CNTn        |

| Ua0n | -> | <b>0PULSE CNTn</b> |

The three counters of this device can be managed through read and write operations to the allocation addresses of registers CNTnH and CNTnL, referring respectively to High and Low bytes of the n-th counter, where n can be in the range 1÷6.

— grifo® ·

### APPENDIX A: COMPONENTS DESCRIPTION

#### Smart Part™

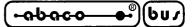

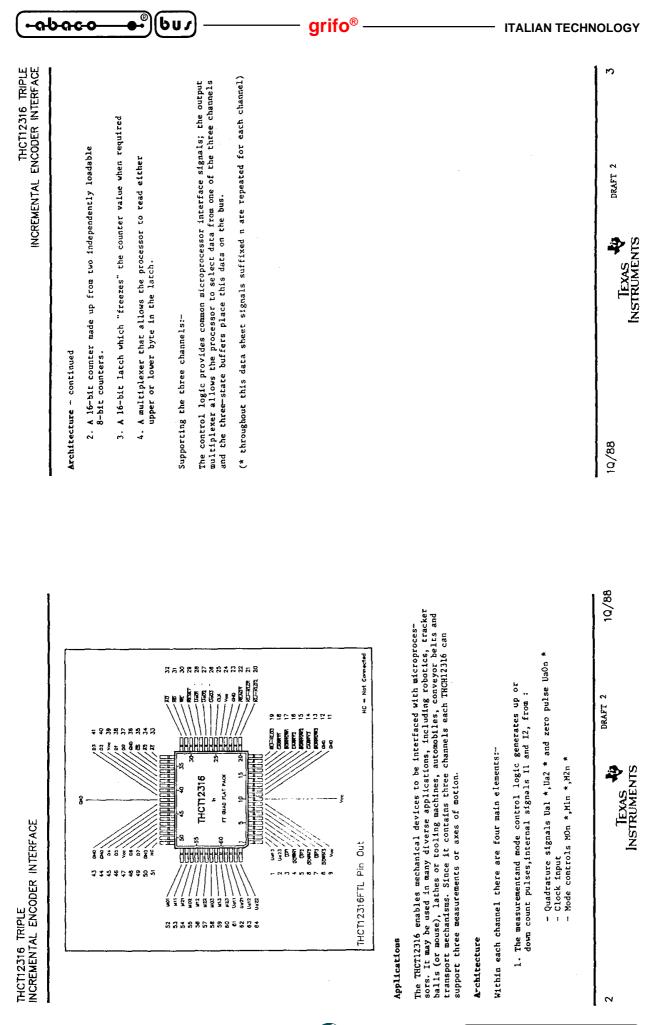

#### THCT12316 TRIPLE INCREMENTAL ENCODER INTERFACE

- Three independent channels in one compact surface mount device

- \* Each channel compatible with the popular THCT2000

- \* Interfaces three mechanisms/ axes to data bus

- Direction discriminators identify & measure forward/ backward rotation/direction

- \* Separate zero pulse input

- Pulse width measurement

- \* Frequency measurement

- \* Cascadable 16-bit counters

- \* TTL compatible

- \* 8-bit parallel 3-state bus

- \* Simple write/read procedure

- Choice of chip carrier or flat package

\* Advanced 1.8um CMOS technology

#### Description

The THCT12316 INCREMENTAL ENCODER INTERFACE consists of three channels each, of which can independently determine the direction and displacement of a mechanical device or axis based on two input signals from transducers in quadrature. Alternatively, each channel can measure a pulse width using a known clock rate, or a frequency, by counting input pulses over a known time interval. It includes three 16-bit counters which may also be used separately. The THCT12316 may be cascaded between channels on one device or between devices to provide accuracy greater than 16-bits, and is designed for use in many types of microprocessor-based systems.

Page A-2

AAC 06

Rel. 5.00

Operation

|               |         |   |                 | COUNTER                                                                                                                                           |

|---------------|---------|---|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 0             | 0       | 0 | 0               | l6-bit up/down counter (inhibits direction<br>discriminator).                                                                                     |

| <br> <br>     |         |   | +               | DIRECTION DISCRIMINATOR                                                                                                                           |

|               | 0       | 0 |                 | Single count pulse synchronous with Ualn<br>rising in forward direction and Ualn<br>falling in backward direction.                                |

| ~~~~~         | 0       |   | 0               | Single count pulse synchronous with Ua2n<br>rising in forward direction and Ua2n<br>falling in backward direction.                                |

| ~~~~ <b>~</b> | 0       | ~ | H               | Double count pulse synchronous.with Ualn<br>rising and falling.                                                                                   |

|               | ~       | 0 | 0               | Double count pulse synchronous with Ua2n<br>rising and falling.                                                                                   |

| بى<br>بى      | +-4<br> | 0 |                 | Quadruple count puise synchronous with all<br>edges.                                                                                              |

|               |         |   | †<br> <br> <br> | PULSE WIDTH MEASUREMENT                                                                                                                           |

| чо<br>чо      | ~1      |   | 0               | Uain is the gate signal<br>Uain is high for up counting and low for<br>down counting.<br>Count is synchronous with rising clock.                  |

|               |         |   |                 | FREQUENCY MEASUREMENT                                                                                                                             |

| ~             | ~       |   |                 | Ualn is frequency signal to be measured<br>Ua2n is the gate signal of known time<br>interval.<br>Count is synchronous with rising edge of<br>Ualn |

**ITALIAN TECHNOLOGY -**

<sub>10</sub>

DRAFT 2

Texas Instruments

10/88

AAC 06

Rel. 5.00

AAC 06

Rel. 5.00

Page A-5

**₽**®

bus

σ

-abaco

| THCT12316 TRIPLE<br>INCREMENTAL ENCODER INTERFACE                                                                                                                                                                                                                                                                        | THCT12316 TRIPLE<br>INCREMENTAL ENCODER INTERFACE                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| operation - continued                                                                                                                                                                                                                                                                                                    | WRITE OPERATION - continued                                                                                                                                                                                                                                                                                                                                                                                                             |

| RESET OPERATION<br>A total reset is initiated by pulling the /RESET pin low. This will clear the<br>counters to zero, reset the D flip-flops at the inputs of the quadrature<br>signals (Ualm and Ua2m), clear the latches that inhibit the load register                                                                | low, and will stay low until /CS and/or /RD go high. The load output register pulse stores the current value of the counter in a 16-bit latch register and /AO directs the selected byte through a multiplexer to the outputs : /CS and /RD also enable the $3-ste$ outputs - see Figure 13. The outputs : /CS and PD loaded immediatel: $12.12/N(11-010)$ is pulled low externally, this signal normally comes from a cascaded device. |

| putse, and load zero into the output register. The should be held to the errors $(+/-1)$ after a reset, the Uain and Ua2n imputs should be held to the values indicated in Table 2 during and just after the reset pulse.                                                                                                | For Modes 6 & 7 see the earlier descripion of these modes.                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                          | Configuration                                                                                                                                                                                                                                                                                                                                                                                                                           |

| MODE   Valn   Va2n<br>0 X X<br>1-5 H Y                                                                                                                                                                                                                                                                                   | Special consideration should be paid to the automatic configuration features<br>of the THCT12316. The purpose of these features is to allow for the different<br>order of byte reads (high then low or low then high) of different processors<br>when doing a word read across a byte wide bus and also to configure cascaded<br>devices automatically for correct word read sequence -see below.                                       |

| <br>;                                                                                                                                                                                                                                                                                                                    | Byte order configuration-                                                                                                                                                                                                                                                                                                                                                                                                               |

| -                                                                                                                                                                                                                                                                                                                        | After a system reset has occured, the first read operation will store the                                                                                                                                                                                                                                                                                                                                                               |

| Table 3                                                                                                                                                                                                                                                                                                                  | value of /AO in a latch within the device. From that time until the next<br>system reset the load output register pulse during a read operation will only<br>to constant of /AO is the constant value. This means that the internal load                                                                                                                                                                                                |

| CASCADING DEVICES                                                                                                                                                                                                                                                                                                        | be generated if /AU is finds stored wature, finds meaning the provident of the particular processor. Special care should be taken if the byte of the particular processor. Special care should be taken if                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                          | reading individual bytes to ensure these operations are always done in a con-                                                                                                                                                                                                                                                                                                                                                           |

| The /KLT-KLOn pins of all cascaded THUTL/16's should be thed together, so<br>that all of the devices load their output registers at the same time. When<br>the 'master' generates a pulse for the other THCTL216's, /KLT-KLON on the                                                                                     | sistent order.<br>Cascaded configuration-                                                                                                                                                                                                                                                                                                                                                                                               |

| as an output, and /ALLALON ON LIE STATES work as Job of one device should be tied to the /UP input of the rie. Similarly, /BORROW should be connected to /DOWN.                                                                                                                                                          | After a system reset the first device and channel to receive a read operation<br>configures itself into "Master" mode and outputs a pulse on /KLI-KLO. In                                                                                                                                                                                                                                                                               |

| Application.<br>READ OPERATION                                                                                                                                                                                                                                                                                           | cascaded operation the /KLI-KLO pins of the cascaded channels are connected<br>together and the input pulse on /KLI-KLO of the cascaded channels configures<br>these to "Slave" mode. On all subsequent read operations the load output res-                                                                                                                                                                                            |

| A number may be preloaded into the counter by pulling /CS and /WE low while<br>using /AO to direct the value on the data bus to the selected byte of the                                                                                                                                                                 | tster pulse is only generated by the "Master" channel (for the appropriate polarity of /A0, as noted above) and this is fed to the "Slave" devices via                                                                                                                                                                                                                                                                                  |

| counter and /A1 & /A2 to select the required channel. This will cause /READY<br>to go low on the next falling clock edge, and remain low until /CS and /WE go                                                                                                                                                            | the /ku/-ku/ connection.                                                                                                                                                                                                                                                                                                                                                                                                                |

| high. See Figure 12.                                                                                                                                                                                                                                                                                                     | Special care should be taken when cascading devices of channels to atrays toom<br>in the same channel order, as well as the byte order already mentioned. To                                                                                                                                                                                                                                                                            |

| WRITE OPERATION                                                                                                                                                                                                                                                                                                          | freeze all three channels with a single read cycle (in cascaded or non-<br>cascaded mode) the /KLI-KLO pins of all channels are connected with a pull-up                                                                                                                                                                                                                                                                                |

| When in MODES 0 to 5 the contents of the counter can be read at any time by pulling /CS and /RD low. The channel is selected by using /AI $\&$ /A2. Within                                                                                                                                                               | resistor to Vcc (see Systems Application). This ensures that only one channel<br>is operating as the "Master" and all others are "Slaves".                                                                                                                                                                                                                                                                                              |

| this channel the most significant byte may be selected be setting /AO to low,<br>and the least significant byte may be read be setting /AO high. This will<br>cause a load output register pulse to be generated and /KLI-KLON will go low<br>during the next low clock pulse. /READY will also go low as the clock goes | If an external "freeze" of the positioning system is required, and external<br>/KLI-KLO pulse will program all channels as slaves. This in derived by gener-<br>ating an external /KLI-KLO pulse before the first read cycle appears after<br>system reset (See Design Checklist).                                                                                                                                                      |

| 10 TEXAS V BRAFT 2 1Q/88<br>INSTRUMENTS                                                                                                                                                                                                                                                                                  | 10/88 TEXAS V DRAFT 2 11<br>INSTRUMENTS                                                                                                                                                                                                                                                                                                                                                                                                 |

AAC 06

Rel. 5.00

••)(bu*s*) -

-abaco

THCT1 INCREI

AAC 06

Rel. 5.00

|              | INTERFACE       |

|--------------|-----------------|

| 12316 TRIPLE | EMENTAL ENCODER |

| • •                                 |                            | Number                                                                                           | 0/1              | Description                                                                                                                                                           |

|-------------------------------------|----------------------------|--------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| +·                                  | PLCC                       | 64<br>QFP                                                                                        | +                |                                                                                                                                                                       |

| /cs                                 | 12                         | 35                                                                                               | Input            | Chip Select. A low enables the device.                                                                                                                                |

| 63/                                 | <i>∞</i>                   | 31                                                                                               | Input            | Read. When this and /CS are active(low),<br>the data from the output register will<br>be present on the data bus.                                                     |

| g · · · ·                           | 14<br>15<br>18<br>18<br>20 | 33<br>45<br>45<br>45                                                                             | Input/<br>Output | LSB<br>Usta Bus Buffer: 8-Bit Bi-directional<br>Duffer with 3-state outputs connected<br>to the microprocessor system.                                                |

|                                     | 5, 23 21                   | 4<br>4<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7 |                  | MSB                                                                                                                                                                   |

| BORROW1<br>BORROW2<br>BORROW3       | 5,5 8                      | 223                                                                                              | Output           | Counter underflow signal                                                                                                                                              |

| /CARRY1<br>/CARRY2<br>/CARRY3       | 54                         | 18<br>16<br>14                                                                                   | Output           | Counter overflow signal                                                                                                                                               |

| /KLI-KL02<br>/KLI-KL02<br>/KLI-KL03 | 62<br>61<br>60             | 21<br>20<br>19                                                                                   | Input/<br>Output | Cascade load input/cascade load output.<br>Open drain output with internal 95uA(nom)<br>pull-up. External pull-up<br>required for full speed operation.               |

| / READY                             | 63                         | 22                                                                                               | Output           | When low signal indicates to the MPU<br>that read or write may be completed.<br>/READY falling edge synchronous with CLK<br>Open drain output needs external pull-up. |

| M11<br>M01                          | 29<br>28<br>27             | 52<br>53<br>54                                                                                   | Input            | Mode select inputs (see Table 1)                                                                                                                                      |

| M22<br>M12<br>M02                   | 34<br>32<br>32             | 55<br>55<br>55                                                                                   | : : :            |                                                                                                                                                                       |

| M23<br>M13<br>M03                   | 36<br>36                   | 9 6 8<br>9 8                                                                                     | ; ; ; ;          |                                                                                                                                                                       |

Texas Instruments

(bu*s*

| THCT12316 TRIPLE<br>INCREMENTAL ENCODER INTERFACE<br>Description |

|------------------------------------------------------------------|

|------------------------------------------------------------------|

| 68 64 1 Input Measuring input signals   13 42 63  (Schmitt characteristics)   13 61  (Schmitt characteristics)   13 64 1 Input Measuring input signals   45 5  (Schmitt characteristics)   13 64     23 28 Input Zero pulse. When active (I   23 28 Input Clock. Used for internal   24 25 Input Clock. Used for internal   26 27 Input Byte select. A high level   9 32 Input Clock. Used for internal   9 32 Input Clock. Used for internal   9 32 Input Clock. Used for internal   9 32 Input Byte select. A high level   10 33 Input Byte select. A high level   11 34 Input Byte select. In the aptropropriate   11 34 Input Byte select. A high level   11 34 Input Byte select. A high level   11 34 Input Byte select. In the counter is cleared   11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 68 64 1 Input Measuring input signals   39 61 " (Schmitt characteristics)   39 61 " (Schmitt characteristics)   43 64 " (Schmitt characteristics)   43 64 " "   43 64 " "   43 64 " "   5 2 Input Zero pulse. When active (low), counter in the appropriate chanter   28 Input Cleared. Other logic is not aff   68 25 Input Clock. Used for internal   68 25 Input Clock. Used for internal   9 32 Input Clock. Used for internal   10 33 Input Clock. Used for internal   11 34 Input Channel select. See Table 2.   11 34 Input Channel select. See Table                                                                                                                                                                                                                                                                                                                                                                          | Pin Name                   | Pin                                                                                              | Number              | 0/1            | Description                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--------------------------------------------------------------------------------------------------|---------------------|----------------|-----------------------------------------------------------------------------------------------|

| 44   1   Input   Measuring input signals     39   61   "   (Schmitt characteristics)     45   2   "   (Schmitt characteristics)     43   64   "   1     41   62   "   Schmitt characteristics)     23   64   "   "     24   27   counter in the appropriate (i counter)   10     27   28   Input   Clock. Used for internal     28   25   Input   Clock. Used for internal     9   32   Input   Sphelronisation and control     9   32   Input   Byte select. A high level     9   32   Input   Selects the most significa     10   33   Input   Channel select. See Table     11   34   Input   Byte select. When active counting     7   30   Input   Byte counter is cleared     7   30   Input   Byte counter is cleared     7   30   Input   Byte counter is cleared     7   30   Input   Byte counter is cleared <th>44   1   Input   Measuring input signals     39   61   "   (Schmitt characteristics)     45   2   "   (Schmitt characteristics)     41   63   2   Input   Zero pulse. When active (low),     27   1   27   counter in the appropriate chan     2   2   Input   Zero pulse. When active (low),     2   2   Input   Clock. Used for internal     2   2   Input   Clock. Used for internal     9   32   Input   Clock. Used for internal     10   33   Input   Channel select. Men active (low)     11   34   Input   Channel select. See Table 2.     11   34   Input   Channel select. See Table 3.     10   <t< th=""><th></th><th>PLCC</th><th>0FP</th><th></th><th></th></t<></th>                                                                                                                                                                                                                                                                                                                 | 44   1   Input   Measuring input signals     39   61   "   (Schmitt characteristics)     45   2   "   (Schmitt characteristics)     41   63   2   Input   Zero pulse. When active (low),     27   1   27   counter in the appropriate chan     2   2   Input   Zero pulse. When active (low),     2   2   Input   Clock. Used for internal     2   2   Input   Clock. Used for internal     9   32   Input   Clock. Used for internal     10   33   Input   Channel select. Men active (low)     11   34   Input   Channel select. See Table 2.     11   34   Input   Channel select. See Table 3.     10 <t< th=""><th></th><th>PLCC</th><th>0FP</th><th></th><th></th></t<>                                                                                                                                                                                                                                          |                            | PLCC                                                                                             | 0FP                 |                |                                                                                               |

| 45   2   "     43   64   "     41   62   "     3   28   Input   Zero pulse. When active (l     2   27   cleared. Other logic is uo     68   25   Input   Clock. Used for internal     9   32   Input   Byte select. A high level     9   32   Input   Byte select. A high level     11   34   Input   Byte select. See Table     11   34   Input   Channel select. See Table     11   34   Input   Selects the most significa     11   34   Input   Control logic is reset to     11   34   Input   Selects the dubt. How Alte counter is cleared     11   34   Input   Control logic is reset to     11   34   Input   Cascade input for counting     29   49   50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 45   2   *     43   64   *     41   62   *     2   27   Counter in the appropriate chan     1   26   27   clared. Other logic is not aff     68   25   Input   Clared. Other logic is not aff     68   25   Input   Clock. Used for internal     9   32   Input   Clock. Used for internal     10   33   Input   Channel select. A high level select     11   34   Input   Channel select. See Table 2.     11   34   Input   Channel select. See Table 2.     11   34   Input   Channel select. See Table 2.     11   34   Input   Channel select. See Table 3.     7   30   Input                                                                                                                                                                                                                                                                                                                                    | Val3<br>Val2<br>Val1       | 44<br>42<br>39                                                                                   | 69 19               | Input:         | Measuring input signals<br>(Schmitt characteristics)                                          |

| 3   28   Input   Zero pulse. When active (1     2   27   counter in the appropriate counter in the appropriate counter in the appropriate synchronisation and control     68   25   Input   Clock. Used for internal     9   32   Input   Byte select. A high level     9   32   Input   Byte select. A high level     10   33   Input   Device reset. When active control     11   34   Input   Channel select. See Table     11   34   100   103   104     11   47   6   100   100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 328InputZero pulse. When active (low),227cleared. Other logic is not aff6825Inputcleared. Other logic is not aff932InputByte select. A high level select932InputByte select. A high level select932InputByte select. A high level select932InputByte select. A high level select1033InputInput1134InputChannel select. See Table 2.1134InputChannel select. See Table 2.1134InputChannel select. Men active (low529InputChannel select. See Table 2.1134InputChannel select. See Table 2.1134InputChannel select. Men active (low529InputCantrol logic is reset to a kno11474Nutte enable. When active (low2496Input3518Input3518Input249513507Power supply volrage 5y +/- lox50710.44,50!Cround.50710.12,23,30!Cround.507144,50!Cround.505011,112,23,30!Cround.5051,11,12,23,30!Cround.                                                                                                                                                                                                                                                                                                                                                                     | Ua23<br>Ua22<br>Ua21       | 4<br>4<br>4<br>4<br>7<br>4<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7 | 64 5<br>65 64 5     | 1 2 4          |                                                                                               |

| 68   25   Input   Clock. Used for internal synchronisation and control synchronisation and control     9   32   Input   Byte select. A high level     10   33   Input   Byte select. A high level     11   34   Input   Channel select. See Table     1   47   6   Input   Control logic is reset to and the counter is cleared     1   47   6   Input   Cascade input for counting     2   49   8   Input   Cascade input for counting     3   50   7   Noter supply voltage 5V +//     51,19,25,111,12,23,30   Cround   Cround   Stond                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6825InputClock. Used for internal<br>synchronisation and control that<br>synchronisation and control that<br>byte select. A high level selec<br>least significant by<br>selects the most significant by<br>least significant by<br>selects the most significant by<br>least significant by<br>selects the most significant by<br>least significant by<br>least significant by<br>least significant by<br>selects the most significant by<br>selects the most significant by<br>least significant by<br>selects the most significant by<br>selects the most significant by<br>selects the most significant by<br>bevice reset. When active (low<br>and /G<br>and the counter is cleared.730InputChannel select. See Table 2.731InputChannel select. See Table 2.733InputChannel select. See Table 2.730InputChannel select. See Table 2.730InputChannel select. See Table 2.730InputChannel select. See Table 2.730InputChannel select. See Table 3.730InputChannel select. See Table 3.730InputChannel select. See Table 3.8496InputCounting down3518InputCascade input for counting up.5079Power supply voltage 5y +/- 10%515,66473Ground.53,6444,50Ground. | /Ua01<br>/Ua02<br>/Ua03    | m 01                                                                                             | 28<br>26            | lnput          | pulse.<br>er in t<br>ed. Oth                                                                  |

| 9   32   Input   Byte select. A Migh level     10   33   Input   least signifucant byte. A selects the most signification     11   34   Input   Channel select. See Table     5   29   Input   Device reset. When active control logic is reset to and the counter is cleared by is loaded into the cunter sective (low), the data tha bus is loaded into the cunting bus is loaded into the cunting bus is loaded into the counting bus is loaded input for counting bus is load bus is loaded input for counting bus is lo                                                                                                                                                                                                                                                                                                                                                                                                                                            | 932InputByte select: A high level select1033Inputleast significant byte. A low<br>selects the most significant by1134InputChannel select. See Table 2.1134InputChannel select. See Table 2.529InputDevice reset. When active (low<br>control logic is reset to a kno<br>and the counter is cleared.730InputWrite enable. When /WE and /GS<br>bus is loaded into the counter<br>red by IAO,IAI and IA3.147446351848550752,6624,39,53,6444,5053,6444,5053,6411,12,23,3653,6411,12,23,3653,6421,11,12,23,3653,6421,11,12,23,3653,6411,12,23,3653,6411,12,23,3653,6411,12,23,3653,6412,43,44,5053,6412,43,44,5053,6412,43,44,5053,6412,43,44,5053,6412,43,44,5053,6412,43,44,5053,6411,12,23,3653,6412,43,44,5053,6412,43,44,5053,6412,43,44,5053,6414,4,5053,6412,11,12,23,3653,6412,11,12,23,3653,6414,4,5053,6412,11,12,23,3653,6414,4,5053,6414,45,605454,44,5055,6112,11,12,1                                                                                                                                                                                                                                                                               | CLK                        | 80                                                                                               | 25                  | Input          | Clock. Used for internal<br>synchronisation and control timing.                               |